一种低功耗、通用、存储容量可变实时信号采集存储方案设计与实现

摘 要:本文介绍了基于Compact Flash Card和TI公司的C24×、C28×系列DSP搭建硬件平台的一种可行的低功耗、通用、存储容量可变实时信号采集存储系统的方案,具体介绍了其硬件连接和相关低功耗软件设计。

关键词:数据采集与存储;低功耗;Compact Flash Card;TMS320LF2407

随着闪烁Flash存储、可编程逻辑器件和数字信号处理器(DSP)芯片制造工艺的进步和性能的不断提高,使数字系统代替了传统模拟系统的同时进一步降低了系统的功耗和体积以满足人们对便携式系统的日益强烈的需求。笔者设计了基于Compact Flash Card和TI公司的C24×、C28×系列DSP搭建硬件平台的一种可行实时信号采集存储系统方案,该系统具有体积小、功耗低、储存容量可变、电路简单、通用、灵活和实用等的特点。TI公司的C24x 系列为16bit定点处理器内置2×8通道10-Bit 数模转换(ADC) 转换时间为500ns, 运算速度为40MIPS,可用于语音、脑电、心电信号等低速数据采集;C28x DSP 系列为32 bit定点处理器内置2×8通道12-Bit ADC转换时间为80ns, 运算速度高达400 MIPS可用于图像信号等高速数据采集。下文以Compact Flash Card(以下简称CF卡)和C24×系列DSP TMS320LF2407硬件平台为例,具体介绍其信号采集系统的硬件平台的搭建和软件省电设计。

1 器件介绍和系统结构框图

1.1 TMS320LF2407芯片简介

TMS320LF2407是TI公司C24x系列中资源最完整的DSP采用高性能静态CMOS技术,25-ns指令周期,速度40-MIPS,低电压3.3V设计;总寻址范围192K字,其中包括64K 程序空间, 64K 数据空间, 64K I/O空间;片内程序空间集成32K字Flash;数据空间集成2.5K字RAM,包括544字DARAM,2K字SARAM;两个事件管理模块EVA、EVB,分别提供两个16-Bits全局计数器,8个脉冲宽度可调调制通道PWM,三个外部事件的定时采样捕获单元;同步的16通道高性能10-bit ADC,转换速率为500ns;串行异步通信接口(SCI)、串行同步外设接口(SPI)、CAN总线2.0接口。由于TMS320LF2407集成了多种数据传输接口,并且片内集成ADC模块,可被广泛用于控制、接口转换以及数据采集等领域。

选择TMS320LF2407作为采集系统的核心处理器的理由:1、片内集成16通道高性能10-bit ADC,不用外扩专用ADC芯片,减少系统的功耗和体积;2、片内程序空间集成32K字Flash,可将系统的控制程序直接烧入到TMS320LF2407片内,不用外扩专用的Flash或EPROM等芯片存放程序,进一步减少系统的功耗和体积;3、低电压3.3V供电,并且片内各功能模块分别单独供电,工作时对没有用到的模块不供电,比如SCI、SPI、CAN总线接口等模块,减少系统的功耗;4、I/O空间寻址范围约64K(255字保留或被占用),资源相当丰富。

1.2 CF卡及各种闪烁存储器简介

市场上常见的闪烁存储器有PC(PCMCIA)、CF(CompactFlash)、SD(SecureDigital)、MMC(MultMedia)、SM(SmartMedia ) 、MS (Memory Stick)以及基于USB接口的闪存等标准。表1比较了这几种闪烁存储器的体积和容量。

CF卡相对别的闪烁存储卡主要有一下优点:容量大,CF最大容量可达2GB以上,满足长时间海量数据的采集要求;性价比高,目前市场上同样容量的卡价格是别的卡系的一半;接口简单,CF卡提供了完整的ATA功能而且通过TrueIDE工作模式兼容IDE接口,可以与TMS320LF2407直接连接;耗电量低,支持在低电压3.3V下工作,使整个系统可用单一电压供电,实际工作电流为30-50mA(和容量有关),支持睡眠模式,睡眠时电流仅为600uA;数据吞吐量高,5V工作时吞吐量为20MB/S,3.3V工作时为6.6MB/S;可靠性高,平均无故障工作时间为100万小时。

1.3 信号采集系统结构框图

系统结构框图主要由图1所示的3部分组成。TMS320LF2407为整个系统的核心数字处理器,其内部的ADC模块完成模数转换并且通过IO空间对CF卡ATA接口以及LCD显示器进行控制;CF卡作为可变容量存储载体存放采集到的数据;LCD用来显示当前的工作状态。整个系统的控制工作、数据的压缩、编解码工作均由TMS320LF2407软件编程实现,使该系统具有很强的通用性和灵活性。

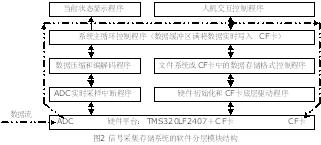

整个系统的控制软件由图2所示的软件模块实现,ADC模块的采样时钟可由TMS320LF2407内部的事件管理模块的GP timers提供。按照数据流的方向整个系统的工作流程:模拟信号经过ADC模块采样,由ADC中断程序将采样结果写入临时缓冲区中再经过压缩或编码送到数据缓冲区中,数据缓冲区满则按照一定数据格式将缓冲区中数据写入CF中。其中数据缓冲区采用双缓存结构交替存放数据以保证将数据无丢失的写入CF卡。

2 系统主要部分接口电路

2.1 CF卡的硬件、软件接口和ATA命令

CF卡遵从ATA协议,为50针接口,可以工作在三种不同模式下:PC卡ATA I/O模式、PC卡ATA Memory模式和TureIDE模式。其中在TureIDE工作模式下重要的信号线有16根数据线(D00-D15),3根地址线(A0-A2),两根寄存器选择线(CS0,CS1),读写控制线(IORD,IOWR),一根中断信号请求线(INTRQ)和一根复位线(RESET)。CF卡存储单元是通过磁头(Head)、柱面(Cylinder)也称磁道和扇区(Sector)组织起来的,在物理寻址(CHS)方式下,每一组H/C/S参数唯一确定存储卡中的一个扇区,通常一个扇区拥有512个字节的数据空间。扇区是最低的寻址单位,其次是磁头,最后是柱面。此外,还有逻辑寻址方式(LBA),在这种寻址方式下,按照以连续序列的逻辑扇区编号进行寻址,下面给出物理寻址方式与逻辑寻址方式的对应关系,设NS为每磁道扇区数,NH为磁头数,C、H、S分别表示磁盘的柱面、磁头和扇区编号,LBA表示逻辑扇区号,Div为整除计算,mod为求余计算则:LBA=NH×NS×C+NS×H+S-1;C=(LBA div NS)div NH;H=(LBA div NS)mod NH;S=(LBA mod NS)+1。

CF内部有多个控制寄存器,通过这些寄存器完成对CF卡的控制。在TureIDE模式下的寄存器组具体功能和地址分配如表2所示。

CF卡的ATA的基本命令有30多条,主要有数据的传输命令,包括扇区、缓冲区的读写等命令;CF卡的定义命令,包括磁道格式化,设置特征参数等命令;电源管理命令,包括检查电源管理模式,进入睡眠省电模式等命令;安全及权限的设置命令等。

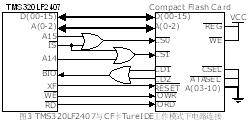

2.2 TMS320LF2407与CF卡的电路连接

TMS320LF2407与CF卡的电路连接如图3所示,CF卡工作在TureIDE模式下,其控制寄存器映射到TMS320LF2407的IO空间地址。地址线A15和A14与IS使能线相或分别控制CF卡的CS0和CS1,则CF卡的控制寄存器的地址为4000H-4007H和8006H、8007H。由于CF卡的CD1和CD2信号线在CF卡内部接地,相或后与TMS320LF2407的BIO相连可以作为CF卡是否插入卡座中的判断依据。TMS320LF2407的XF管脚与CF卡的RESET信号线相连可以实现CF卡的软件复位,保证CF卡工作在TureIDE模式下。由于TMS320LF2407的读写控制线比较丰富,可将RD和WE作为CF卡的读写信号线。另外,在对CF卡进行控制几乎用不到CS1信号线为低的情况,可将控制线接高电平,省下一个逻辑或门。TMS320LF2407与CF卡连接不需要任何接口转换芯片,逻辑电路仅需要2-3个或门,如此简单的接口电路也是其它类型的闪烁存储卡所不能比拟的。

3 系统关键软件编程汇编实现实例

3.1 TMS320LF2407与CF卡ATA接口TI公司DSP汇编程序实例

考虑到TI公司的DSP各系列芯片汇编指令的兼容性便于跨平台移植和汇编语言代码高效性,下面给出基于上连接框图将从CF卡中一扇区数据(512字节)读到TMS320LF2407片内RAM中的DSP汇编函数程序清单:

READ_A_SECT:

W_CF_RDY: ;检测CF卡是否空闲

LDP #0h;将页面指针赋0,用于直接地址访问

IN CF_IN,CFCOM_STAT;读取状态寄存器内容

LACL CF_IN ;CF_IN为数据空间的变量

AND #00FFh;仅低8位为有效数据位

XOR #50h;判断当前状态寄存器值是否等于50h

BZ END_WAIT_RDY;CF卡空闲

B W_CF_RDY;继续等待CF卡空闲

END_WAIT_RDY: ;写控制寄存器

SPLK #0h,CF_OUT;CF_OUT为数据空间的变量

OUT CF_OUT,CFERR_FEA;将0h写入特征寄存器

SPLK #1h,CF_OUT;1h表示一次仅读写一个扇区

OUT CF_OUT,CFSEC_COU;将1h写入扇区数寄存器

SAR AR3,CF_OUT;A3为辅助寄存器,作为入口参数

OUT CF_OUT,CFSEC_NO;写扇区号寄存器

SAR AR4,CF_OUT;A4为辅助寄存器,作为入口参数

OUT CF_OUT,CFCYL_LOW;写柱面号寄存器(低字节)

SAR AR5,CF_OUT;A5为辅助寄存器,作为入口参数

OUT CF_OUT,CFCYL_HIG;写柱面号寄存器(高字节)

SAR AR6,CF_OUT;A6为辅助寄存器,作为入口参数

OUT CF_OUT,CF_CDH;写驱动器选择/磁头寄存器

SPLK #20h,CF_OUT;20h为读扇区ATA命令

OUT CF_OUT,CFCOM_STAT;写命令寄存器

W_CF_DRQ: ;检测CF卡是否处理完毕命令并且有数据请求

IN CF_IN,CFCOM_STAT;读取状态寄存器内容

LACL CF_IN;CF_IN为数据空间的变量

AND #00FFh;仅低8位为有效数据位

XOR #0058h;判断当前状态寄存器值是否等于58h

BZ END_WAIT_DRQ;CF有数据请求

B W_CF_DRQ;继续等待CF卡的数据请求

END_WAIT_DRQ:循环将该扇区数据内容读到2407的RAM中

LAR AR2,#0FFh;作256次循环读取256字数据

MAR *,AR1;将辅助寄存器AR1作为间接寻址寄存器

INLOOP:IN *+,CFDATA,AR2;读取CF卡数据寄存器

BANZ INLOOP,*-,AR1;循环读取数据控制

RET ;结束返回

程序说明:CFDATA为数据寄存器端口地址;CFCOM_STAT为状态/命令寄存器端口地址;CFERR_FEA为特征寄存器端口地址;CFSEC_COU为扇区数寄存器端口地址;CFSEC_NO为扇区号寄存器端口地址;CFCYL_LOW为柱面号寄存器(低字节)端口地址;CFCYL_HIG为柱面号寄存器(高字节)端口地址;AR1,AR3-AR6辅助寄存器为程序入口参数,其中AR1为RAM数据缓冲区的起始地址,AR3-AR6为CF卡各寄存器待赋的值;CF_IN和CF_OUT为变量。鉴于篇幅,程序中没有进行超时处理。

3.2 TMS320LF2407的堆栈处理DSP汇编程序实例

由于TMS320LF2407只有8级硬件堆栈,如果进行8级以上函数或中断调用就会产生堆栈溢出,为了保证系统软件的工作的稳定性和正确性并且方便函数调用进行参数传递和临时变量的存放,必须自己定义堆栈。笔者用非常简洁的方法实现TMS320LF2407的堆栈处理:将地址0200-02FF和0300-03FF的数据空间分别作为系统函数调用和中断函数的堆栈段,其栈底固定,辅助寄存器AR0和AR7分别作为其堆栈顶指针。为了保证数据采样的实时性,采用双堆栈设计使系统函数调用出入堆栈不必关闭系统中断。下面给出中断调用时相关寄存器入栈和出栈的DSP汇编程序清单,函数调用与此类似:

Interrupt_Entry: ;进入中断程序2407自动关闭可屏蔽中断

MAR *,AR0;将堆栈指针AR0作为间接寻址指针

SST #1,*+;将ST1寄存器内容压入堆栈

SST #0,*+;将ST0寄存器内容压入堆栈

POPD *+;将硬件堆栈栈顶出栈并将其值压入软件堆栈,防止硬件堆栈溢出

SACL *+;将ACC寄存器低16位数据压入堆栈

SACH *+;将ACC寄存器高16位数据压入堆栈

SAR AR1,*+;将AR1寄存器内容压入堆栈

SAR AR2,*+;将AR2寄存器内容压入堆栈

SAR AR3,*+;将AR3寄存器内容压入堆栈

SAR AR4,*+;将AR4寄存器内容压入堆栈

SAR AR5,*+;将AR5寄存器内容压入堆栈

SAR AR6,*+;将AR6寄存器内容压入堆栈

SAR AR7,*+;将AR7寄存器内容压入堆栈

CLRC INTM;使能中断,允许中断嵌套

…

…;具体中断程序

…

SETC INTM;关闭中断,防止出栈时有中断产生

MAR *,AR0;将堆栈指针AR0作为间接寻址指针

SBRK #1;将AR0内容减1

LAR AR7,*- ;恢复AR7寄存器的值

LAR AR6,*- ;恢复AR6寄存器的值

LAR AR5,*- ;恢复AR5寄存器的值

LAR AR4,*- ;恢复AR4寄存器的值

LAR AR3,*- ;恢复AR3寄存器的值

LAR AR2,*- ;恢复AR2寄存器的值

LAR AR1,*- ;恢复AR1寄存器的值

LACC *-,16;恢复ACC寄存器高16位的值

ADD *- ;恢复ACC寄存器低16位的值

PSHD *-;将硬件堆栈栈顶值压回硬件堆栈,用于中断程序返回

LST #0,*-;恢复ST0寄存器的值

LST #1,*;恢复ST1寄存器的值

CLRC INTM;使能中断

RET ;中断程序返回

3.2 TMS320LF2407的ADC相关寄存器设置DSP汇编程序实例

TMS320LF2407片内集成16通道高性能10-bit ADC,转换时间为500 ns,ADC模块的采样时钟的控制很灵活,可以由TMS320LF2407内部的事件管理器的GP timers以多种方式提供。以Timer1为例说明相关寄存器的设置,采样时钟的频率由Time1的周期寄存器控制,其具体参数请参见TMS320LF2407手册:

LDP #GPTCONA >> 7h;设置页面指针,用于直接地址访问

SPLK #3h,GPTCONA;设置GP timer全局控制寄存器

SPLK #0F42h,T1CON;设置Time1的控制寄存器

SPLK #**h,T1PR;设置Time1的周期寄存器,确定采样频率

LDP #ADCL_CNTL1>>7h;设置页面指针,用于直接地址访问

SPLK #4000h,ADCL_CNTL1;复位ADC模块

SPLK #2010h,ADCL_CNTL1;设置ADC控制寄存器1

SPLK #15,MAXCONV;最大通道数16

SPLK #03210h,CHSELSEQ1;设置通道顺序控制寄存器1

SPLK #07654h,CHSELSEQ2;设置通道顺序控制寄存器2

SPLK #0BA98h,CHSELSEQ3;设置通道顺序控制寄存器3

SPLK #0FEDCh,CHSELSEQ4;设置通道顺序控制寄存器4

SPLK #0B0Ah,ADCL_CNTL2;设置ADC控制寄存器2

LDP #GPTCONA>>7h;设置页面指针,用于直接地址访问

SPLK #100h,GPTCONA;使能timer1周期中断启动ADC

4 系统软件省电设计

除了选择低功耗的器件和简化硬件平台的搭建之外,在系统软件设计上能够进一步降低系统的功耗。其软件设计虽然简单但结果非常令人满意往往能减少系统50%以上的功耗,主要在于减少CF卡和DSP的功耗。

4.1 降低CF卡功耗的软件设计

降低CF卡功耗的理论依据:CF卡支持睡眠模式,睡眠时电流仅为600uA,任一命令均能唤醒CF卡,唤醒时间小于200ns。可以利用ATA命令E1h或95h强迫CF卡进入睡眠模式。软件可以这样设计:在对CF卡进行扇区读、写程序结尾,在CF卡控制命令寄存器里写入E1h或95h命令,使CF卡立即进入睡眠模式即可,这样CF卡在进行数据传输之外的时间里保持睡眠模式,在很大程度上节省了系统的功耗。

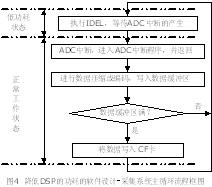

4.2 降低DSP功耗的软件设计

降低DSP功耗的理论依据:利用TI公司C2××系列DSP汇编指令IDEL,执行该指令使DSP进入低功耗模式并等待中断的产生。采集系统的主循环程序往往可能在等待数据缓冲区满而消耗大量的空闲时间,如果将在这些等待时间里让DSP进入低功耗模式将会节省相当程度的功耗,其软件设计框图如图4所示。(注:早期的TMS320LF2407与后来的TMS320LF2407A在执行IDEL指令上有所不同,TMS320LF2407执行IDEL指令需要非屏蔽中断才能唤醒,而对于TMS320LF2407A可屏蔽中断也能唤醒,因此降低DSP的功耗程序进对TMS320LF2407A有效。)

结束语

由于C24×、C28×系列DSP与CF卡接口电路简单,可以单一3.3V电压供电,所有系统控制和功能扩展均由可软件实现,并且CF卡的容量可变且容易与PC机进行数据交换。因此采用TI公司的C24×、C28×系列DSP与CF卡搭建数据采集存储的硬件平台,具有硬件电路简单、功耗低、通用性很强、容量可变等优点,有很高的实用价值适用于很多情况下的数据采集存储。