Atmel ATR0630P1GPS接收方案

Atmel 公司的ATR0630P1是低功耗单片GPS接收器,特别设计用于移动应用.它采用Atmel®的 ANTARIS 4技术,集成了RF前端,滤波器和基带处理器,具有低功耗和低噪音,并提供极好的RF性能:采集灵敏度-140dBm,跟踪灵敏度-150dBm.本文介绍了ATR0630P1接收器的主要特性,方框图和外部应用连接案例.The ATR0630P1 is a low-power, single-chip GPS receiver, especially designed to meet the requirements of mobile applications. It is based on Atmel®’s ANTARIS®4 technology and integrates an RF front-end, filtering, and a baseband processor in a single, tiny 7 mm x10 mm 96 pin BGA package. Providing excellent RF performance with low noise figure and low power consumption.

Due to the fully integrated design, just an RF SAW filter, a GPS XTAL (no TCXO) and blocking capacitors are required to realize a stand-alone GPS functionality.

The ATR0630P1 includes a complete GPS firmware, licensed from u-blox AG, which performs the GPS operation, including tracking, acquisition, navigation and position data output. For normal PVT (Position/Velocity/Time) applications, there is no need for external Flash- or ROM-memory.

The firmware supports e.g. the NMEA protocol (2.1 and 2.3), a binary protocol for PVT data, configuration and debugging, the RTCM protocol for DGPS, SBAS (WAAS, EGNOS and MSAS) and A-GPS (aiding). It is also possible to store the configuration settings in an optional external EEPROM.

Due to the integrated ARM7TDMI processor and an intelligent radio architecture, the

ATR0630P1 operates in a complete autonomous mode, utilizing on chip AGC in closed loop operation

ATR0630P1主要特性:

16-channel GPS Correlator

8192 Search Bins with GPS Acquisition Accelerator

Accuracy: 2.5m CEP (2D, Stand Alone)

Time to First Fix: 34s (Cold Start)

Acquisition Sensitivity: –140 dBm (With External LNA)

Tracking Sensitivity: –150 dBm (With External LNA)

Utilizes the ARM7TDMI ARM Thumb Processor Core

High-performance 32-bit RISC Architecture

EmbeddedICE™ (In-Circuit Emulation)

128 Kbytes Internal RAM

384 Kbytes Internal ROM with u-blox GPS Firmware

1.5-bit ADC On-chip

Single IF Architecture

2 External Interrupts

24 User-programmable I/O Lines

1 USB Device Port

Universal Serial Bus (USB) 2.0 Full-speed Device

Embedded USB V2.0 Full-speed Transceiver

2 USARTs

Master/Slave SPI Interface

4 External Slave Chip Selects

Programmable Watchdog Timer

Advanced Power Management Controller (APMC)

Geared Master Clock to Reduce Power Consumption

Sleep State with Disabled Master Clock

Hibernate State with 32.768 kHz Master Clock

Real Time Clock (RTC)

1.8V to 3.3V User-definable IO Voltage for Several GPIOs with 5V Tolerance

4 KBytes of Battery Backup Memory

7 mm × 10 mm 96 Pin BGA Package, 0.8 mm Pitch, Pb-free, RoHS-compliant

ATR0630P1优势:

Fully Integrated Design With Low BOM

No External Flash Memory Required

Requires Only a GPS XTAL, No TCXO

Supports NMEA, UBX Binary and RTCM Protocol for DGPS

Supports SBAS (WAAS, EGNOS, MSAS)

Up to 4Hz Update Rate

Supports A-GPS (Aiding)

Excellent Noise Performance

图1. ATR0630P1方框图

图2. ATR0630P1外部应用连接案例

相关推荐

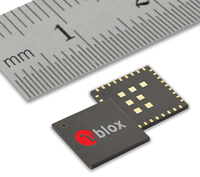

u-blox发布全球最小的独立式定位模块EVA-M8M

2014-11-09

在线研讨会

焦点