PCB导线设计技术(下)

前两集中介绍了微电脑周边、模拟电路基板、宽频与高频电路基板、电源与功率电路基板,以及数字电路基板导线设计,本篇将接着说明Video应用电路基板导线设计。![]() 宽频数十MHz video增幅电路图案的设计技巧

宽频数十MHz video增幅电路图案的设计技巧

模拟信号尤其是类似0~数十MHz video信号宽频电路时,电路图上详细标示信号的流动路径与元件位置非常重要。图56是电流復归型video用OP增幅器HA-5020构成的影像增幅电路(video amplifier)。传统电压復归型OP增幅电路,gain一旦变大时频宽会降低,相较之下电流復归型OP增幅电路,由于理论上频宽取决于復归阻抗值决,因此不受gain的影响可以获得较大频宽。如图56所示从左侧输入的video信号,利用 (HA-5020)构成的OP增幅器增幅2倍之后输出至右侧。

图57是频宽数十MHz的影像增幅电路基板图案,频率一旦进入影像频宽范围时,电路基板的设计直接影响电路特性,尤其是最短距离的连接,同时沿着电路图的流动路径设计基板图案非常重要。根据以上观点比较图56与图57时,可以确定信号的流动路径与元件的设置,几乎与图56电路图完全一致

若影像增幅电路使用晶片型元件,一般比较容易获得预期的动作特性,如果使用传统导线元件,导线的电感成份可能会影响电路特性。

如图56所示提供IC的电源与接地之间插入旁通电容(bypass condenser),此外图56与图57IC脚架附近分别插入47μF电解电容,与并联的0.1μF、0.01μF陶瓷电容,接着再用粗短图案连接,由于受限于元件封装空间,因此等元件封装在图57电路基板的背面。

如图58(a)所示电源供给源与接地之间插入旁通电容,如果从58(b)IC的右侧插入,就无法发挥旁通电容的功能。

![]() D-A converter周边模拟-数字电路的布线图案分离技巧

D-A converter周边模拟-数字电路的布线图案分离技巧

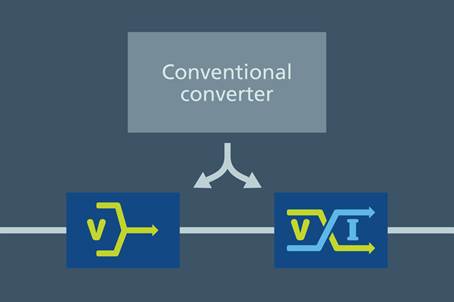

D-A converter与后述的数字影像编码器(digital video encoder),是模拟介面输出不可或缺的LSI,由于基板上混载模拟与数字信号,因此电路基板图案的设计非常重要。

此处以SONY开发的8位元,40MSPS高速D-A converter CXD1171M为例,介绍电路基板图案设计技巧。图59是CXD1171M 40MSPS高速D-A converter的电路图;图60是使用3个影像用D-A converter CXD1171M的周边电路基板图案。

设计模拟与数字电路混载的基板图案时,必需注意两电路的隔离(isolation),如果隔离不完全会发生crosstalk,以及数字电路的噪音(noise)重叠至模拟电路等现象,因此设计阶段必需考虑元件与布线数量,最后才能决定模拟与数字电路block的大小与位置(图61),元件则分别封装在各block内,接着进行图案布线Layout。

设计上避免信号图案贴近数字信号图案或是两信号图案平行并排,如果基板结构两信号图案有邻近之虞时,图案之间必需插入接地图案(ground pattern),藉此分隔两信号(图62)。

以上介绍单面电路基板布线图案设计技巧;双面电路基板的场合必需检查数字电路图案是否与模拟电路图案交叉、重叠,图案层间尽量插入接地层,同时还需使用具备遮蔽(shield)效果的4层以上多层电路基板;模拟电源与数字电源由基板上相同电源提供时,尽量由低阻抗电源连接单元提供。

![]() 可确保模拟信号精度的数字影像编码器电路基板图案

可确保模拟信号精度的数字影像编码器电路基板图案

图63是数字影像编码器ADV7194与周边的电路图;图64是数字影像编码器与周边电路基板图案。数字影像编码器主要功能是将数字影像资料转换成组合(composite)信号与Y/C等模拟影像信号。

图63电路图中的ADV7194会针对27MHz高速时脉(clock),输入数字信号进行数字编码器,接着再从高精度10位元D-A converter输出模拟影像信号。一般影像编码器等D-A转换电路或是A-D转换电路,为降低噪音通常会将模拟与数字的接地分开,此时基于两接地的电位能变成一致等考量,尽量靠近IC附近作单点连接。不过本电路并未作单点连接,而是利用Ferrite beads防止数字接地的噪音流入模拟接地。

如图64所示ADV7194左侧的44~58 pin变成模拟信号,其它三边的脚架则变成数字信号,此处必需注意两信号的导线图案不可平行或是交叉,此外模拟信号系需作full ground,因此ADV7194左侧与内层为full ground结构。

随着频率高频化接地的阻抗也大幅增加,数位电路的信号越高速噪讯量也越多,模拟信号微小变化可能会因为噪音的渗入无法获得预期的精度,为了使类似ADV7194高速、高精度IC发挥功能,因此必需降低基板图案的接地阻并抗抑制噪音。

降低基板图案的接地阻抗可以采用full ground设计,双面电路基板的场合,元件尽量作单面封装,背面作full ground设计;高密度封装却无法作full ground设计时,元件可以封装在宽度较大的图案上(图65),虽然这种方法可以有效降低阻抗,不过反面缺点是噪音处理相当棘手。

成本允许的范围下建议改用多层电路基板,因为内层基板具有电源层、接地层结构,所以多层电路基板可以降低电源与接地的阻抗;基板表层无法布线、内层基板有布线图案设计,或是利用复数的电源电压细分电源层时必需增加基板层数,类似图64的场合建议使用6层电路基板。各数字IC的时脉端子为了减轻反射波的影响,一般会使用图66的笔直性图案连接,元件的封装设计则需考虑时脉信号图案的Layout方便性。

![]() 可精确传输25~165Mp/s差动介面的电路基板图案

可精确传输25~165Mp/s差动介面的电路基板图案

99年DDWG(Digital Display Working Group)正式公佈的DVI(Digital Visual Interface)规范,DVI主要应用在PC与显示器之间的影像传输,尔后随着HDMI(High Definition Multimedia Interface)规格化之后,DVI立即被HDMI取代,成为消费性电子产品数字介面主流,不论事DVI或是HDMI内部都设有保护digital contents的HDCP(High-bandwidth Digital Content Protection)。DVI的影像传输使用Silicon Image公司开发的TMDS(Transition Minimized Differential Signaling)ring技术,TMDS可分为single ring与dual ring两种。

一个画素资料24位元(R、G、B各8位元),加上2位元同步信号与4位元控制资料,变成30位元再经过编码处理后,转换成三频(channel)10位元serial数字信号,三频信号依照画素时脉(pixel clock)以4对(pair)差动信号传输时称为single ring(图67)。

single ring传输极限大约是162Mp/s(UXGA)(p/s: pixel/second),超过该速度传送影像,必需改用dual ring方式。dual ring使用6频,它会随着画素时脉传,输两画素资料48位元(R、G、B各8位元×2画素)、10位元控制资料。图68是TMDS传送器(transmitter) LSI SiI164构成的DVI送信电路。

图69是上述传送器的电路基板基板图案。设计DVI送信电路基板基板图案时,必需注意传送器的输出布线图案,由于传送器的各输出频道属于差动信号对(pair),虽然差动信号对不易受噪音影响,而且噪音的释放非常少,不过布线图案设计不当时就无法发挥上述特征,因此差动信号对尽量邻近设置,即使噪音重叠变成common mode也会被接收器抵销,而且抵销时还会朝抵销磁界的方向,因此可以抑制噪音的放射(图70)。

差动信号对之间必需维持一定的距离,同时还需整合pair的Layout位置与导线的弯曲位置,因为pair之间维持均衡对差动传输非常重要。差动信号的导线长度必相同,如果长度不同时会产生传输延迟(skew)现象,一旦位相偏移就无法抵销磁界音放射量则大幅增加(图71)。

包含差动信号在内几乎所有高速信号的布线图案,都非常忌讳直角或是锐角弯曲设计,为降低阻抗变化佈线图案通常都采用 或是曲线弯曲设计。DVI稳定传输要素除了送信电路之外,缆线(cable)与收信电路也需列入检讨,例如使用twist pair twinax等平衡缆线等等。此外收信电路从输入连接器(connector)到接收器LSI之间的佈线图案设计注意事项,与上述送信电路佈线图案完全相同。

![]() 同轴缆线作1.485Gbps传输的电路基板图案

同轴缆线作1.485Gbps传输的电路基板图案

所谓SDI(Serial Digital Interface)是指将影像信号转换成serial数字信号传输的介面而言。4:2:2的元件(component)传输率为270Mbps,HDTV则高达1.485Gbps。由SDI构成的电路可以利用电视播放台内的同轴缆线,传输高解析度的影像资料,除此之外它还可能在辅助性(ancillary)影像资料间隙领域,重叠传输audio资料、字幕资料,以及播放台之间的资料。

有关HDTV的serial数字介面,在SMPTE 292规范中有详细说明,虽然分成同轴缆线介面与光纤介面两种,不过此处以Gennum公司的IC为例,介绍使用同轴缆线的介面器。

图72是HDTV serial digital serialize GS1522、VCO GO1515,与HDTV缆线驱动器GS1508构成的SDI送信单元的电路图;图73是SDI送信单元的电路基板图案。GS1522是SMPTE 274M、SMPTE 260M的parallel数字资料,转换成SMPTE 292M serial数字信号的IC,该IC可以支援1.485Gbps与1.485/1.001Gbps;GO1515则是组合serialize与接收器(receiver)的电压控制振荡器VCO,它可以接收GS1522的控制电压,产生1.485GHz或是1.485/1.001GHz的基准时脉给GS1522。

封装时GS1522设在基板背面,同时尽量缩短导线长度,GS1508可以和Gennum公司的IC连接使用,不过也可以当作一般驱动器使用,它是具备两条75Ω的同轴缆线的缆线驱动器。SDI的输出属于1.485Gbps高速传输线路,本电路基板为了降低寄生容量,所以取消输出元件与布线图案下方的接地设计。

如果布线图案长度超过1cm时,必需使用micro strip line作特性阻抗整合,1.485Gbps高速传输时,无法沿用传统的元件与基板处理方式,元件的寄生容量与寄生电感(inductance)必需视为元件范畴处理,在此同时佈线图案必需当作分散封装的电阻、电容、电感来处理,类似这样将布线图案当作元件处理的电路称为「分布定数电路」。分佈定数电路中经常使用micro strip line。

图74是micro strip line的结构,micro strip line的特性组抗与电路整治,可以作低损失(loss)的的资料传输。特性阻抗(impedance)是由佈线图案的宽度、电路基板图案厚度

、电路基板厚度

,以及电路基板材料的比诱率

决定。特性阻抗 可用下列计算式求得:

设计SDI输出电路必需注意return loss,虽然SMPTE 292M规范与ARIB BTA-S-004B规范的内部有些差异,不过两者都有限度值的规定。return loss主要是表示阻抗值不整合时的反射波大小,反射值越大表示反射波越小特性越好。

实际上电路基板或是电子设备组装后,利用网路分析仪(analyzer)测试return loss,如果测试结果不如预期一般只能改变图72电路图中的的值或是重新制作电路板,因此笔者建议设计电路基板时,最好作电脑模拟分析检讨。