基于ADSP-BF561的H.264编码器设计

0 引 言

互联网的带宽越来越大,基于互联网的信息特别是声音图像实时数据的传输已经成为可能。视频和音频数据的传输正好充分利用了互联网带宽,并达到了实时交流以及进行远程开会的可能。视频会议系统相比传统的电话会议更充分利用了互联网资源,从而降低了运营成本。

视频编码器是视频会议系统的主要构成部分。目前视频压缩标准有H.261、H.263、MPEG4和H.264等。新一代视频编码标准H.264与以往标准相比具有压缩率高,网络亲和性好,视频质量优越等优点。H.264引入了许多当前视频编码中的新技术,使得在相同的重建图像质量下,编码效率比H.263和MPEG-4高50%左右。因此,视频编码器设计中采用了H.264编码标准,编码器主要通过美国AD公司的BF561 DSP芯片实现。目前,视频处理方案也已经由前几年的ASIC方案转向DSP平台。在DSP平台上进行视频产品开发有以下几方面的优势:第一,用户开发自由度更大,支持多种个性化开发,可以适应市场不断提出的新要求,在第一时间提升产品性能,增强产品的竞争能力;第二,DSP处理能力强,可以在一个DSP上同时实现多路音、视频信号的压缩处理;第三,开发周期短,能实现快速技术更新和产品换代,各种新出现的快速及优化算法可灵活进行升级。

1 BF561介绍

BF561采用了对称双核的架构,在一颗BF561芯片内部集成了2个BF533 DSP内核,2个内核主频都可以高达600 MHz,支持并行处理。BF561处理器的特性保证了其强大的数字信号处理能力,并且支持低电压低电流供电,能够满足多功能的数字消费类产品对于性能、功耗方面的要求。

1.1 DMA介绍

Blackfin处理器用直接存储器访问(DMA)在存储器之间或存储器与外设之间传送数据。DMA控制器可在存储器和片上外设(外设DMA)之间进行数据传送,以及在L1/L2/L3存储器间进行数据传送(存储器DMA或MDMA)。DMA控制器是Blackfin处理器架构中的重要组件,完全独立于内核,不会进行周期挪用,完全无需占用处理器内核周期。在理想的应用配置中,内核只需要设置DMA控制器,并在数据调用过程中响应中断。

BF561有3个独立的DMA控制器DMA1,DMA2和IMDMA。DMA1和DMA2控制器各有12个外设DMA通道和4个存储器DMA通道。IMDMA控制器有4个存储器DMA通道。

1.2 基于描述符的DMA

基于描述符的DMA传送需要存储于存储器中的参数来初始化一个DMA队列。描述符包括所有需对DMA控制寄存器正常编程的参数。描述符允许把多个DMA队列链接在一起。在基于描述符的DMA操作中,可以对一个DMA通道编程,以便在当前传送队列完成后,自动设置和启动其他DMA传送过程。在管理一个系统的DMA传送过程时,基于描述符的模型能提供最大的灵活性。

描述符列表模型分为描述符列表“小”模式和描述符列表“大”模式。在描述符列表“小”模式中,描述段包括一个16位字段,用以指向下一描述符入口地址的低16位,地址的高16位通过寄存器编程得到且保持不变,限制描述符在存储器的一个特定64 KB大小的页中。当描述符需要跨页时,可用能提供32位入口地址的描述符列表“大”模式。

2 H.264视频编码器构成

H.264编码器由视频采集、数据格式转换、H.264编码3部分组成。视频采集部分负责捕获图像,并且将捕获到的图像通过PPI接口填充到指定的视频帧缓冲区中。数据格式转换部分完成将输入的4:2:2格式的图像转换成H-264编码器能够编码的4:2:0格式的数据。H.264编码部分负责对4:2:0格式图像编码。

在本视频编码器设计中,BF561 A核用于运行操作系统和协议栈,而H.264算法在B核实现。

2.1 视频采集

视频采集是由摄像头OV7660完成,OV7660是美国OmniVision公司开发的一款CMOS彩色图像传感器芯片,支持VGA,QVGA,GIF等多种分辨率。视频输出格式有Raw RGB,GRB 4:2:2和YUV/YCb-Cr(4:2:2)。在本设计中,选择CIF YVYU(4:2:2)格式,需要设置其相应寄存器COMl=0X00,CLKRC=OX80,COM7=0X30,TSLB=0X05。摄像头配置完后,打开PPIO将视频数据填充到Blackfin处理器的视频帧缓冲区中。采用基于描述符的PPI DMA可以很容易的实现乒乓缓冲,从而确保不会覆盖尚未处理完毕的输入数据。

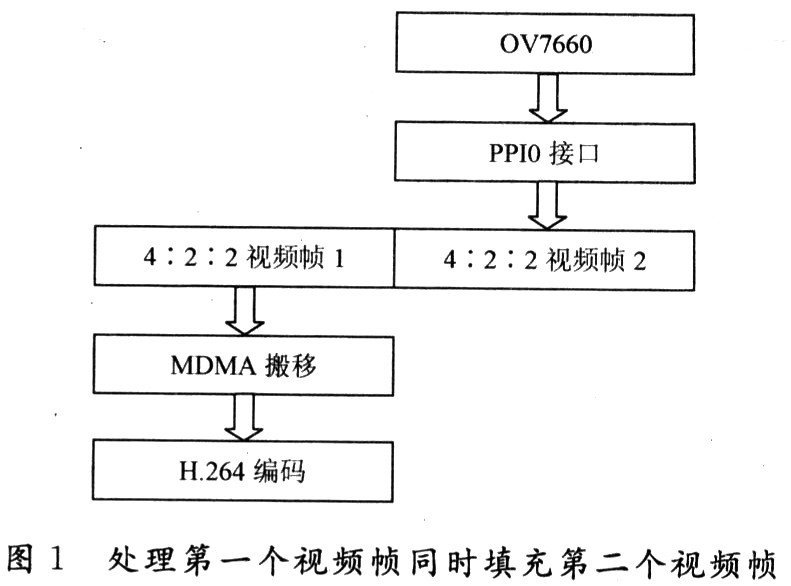

乒乓缓冲的原理如图1所示。

设置两个CIF 4:2:2帧大小的输入缓冲区,首先输入数据通过PPI接口填充到4:2:2视频帧1中,当第一帧数据填充满时,处理器对这帧数据进行MDMA搬移和压缩编码等操作,与此同时,PPI继续填充第二个视频帧。当第二个视频帧填充满时,处理器处理第二个视频帧同时填充第一个视频帧。利用乒乓缓冲,数据将源源不断地填充到两个视频帧中。

2.2 数据格式转换

视频采集到的图像是交织的4:2:2格式的YUV视频数据,而H.264视频编码算法对4:2:O格式的视频数据进行压缩。4:2:O格式数据的亮度值缓冲区和色度值缓冲区是分离的,利用MDMA搬移,可以实现亮度缓冲区和色度缓冲区的分离。

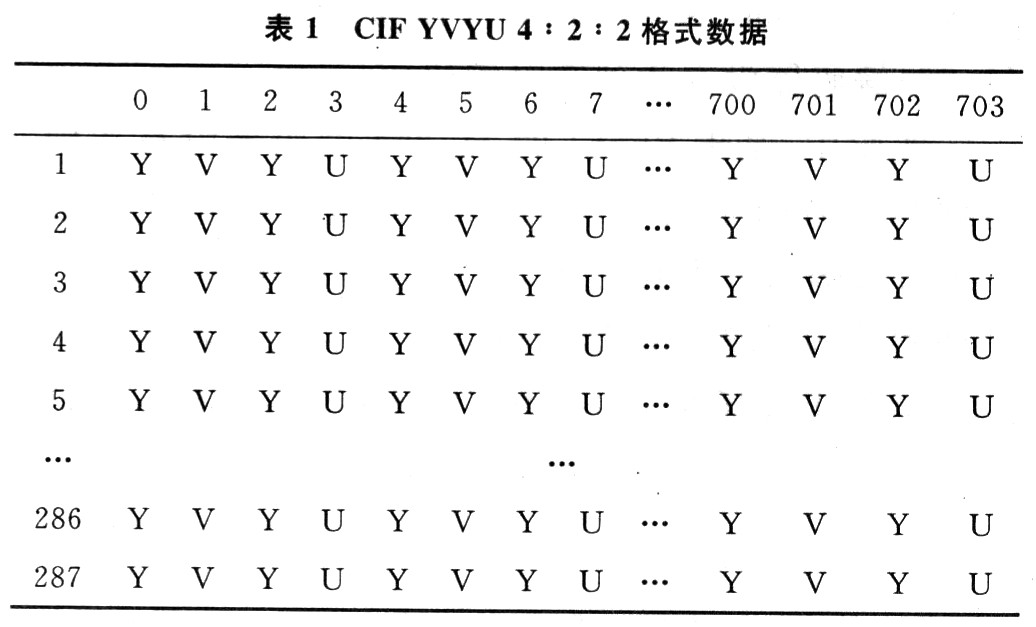

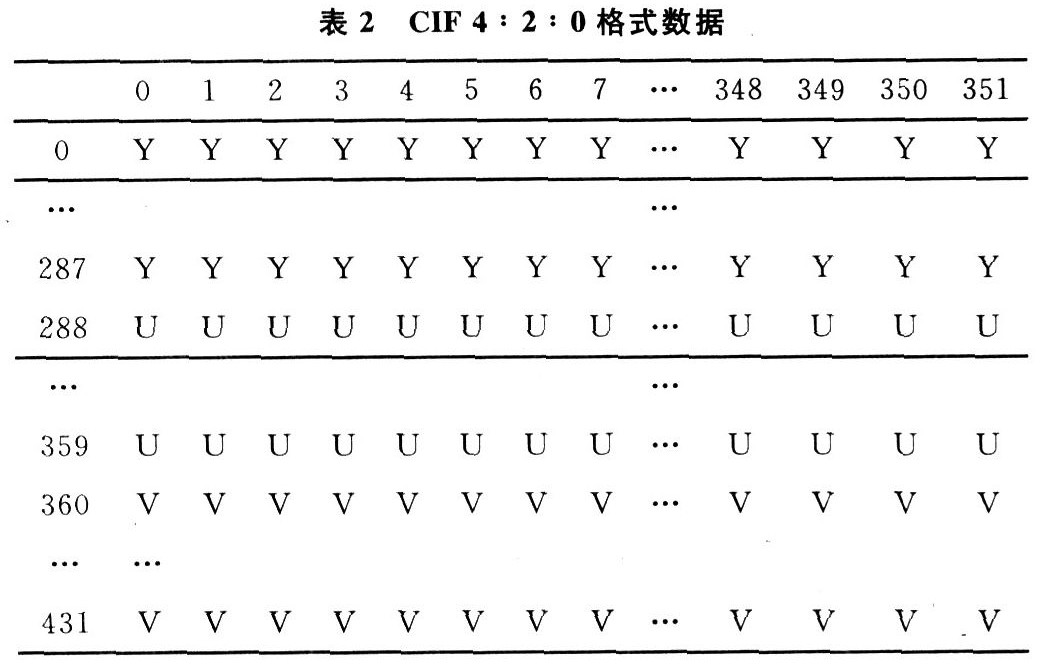

CIF YVYU(4:2:2)格式数据如表1所示,CIF 4:2:O格式数据如表2所示。4:2:2格式图像一个宏像素中有4个Y分量,2个U分量和2个V分量[8]。4:2:0格式图像一个宏像素中有4个Y分量,1个U分量和1个V分量。Y,U和V的存储区是分开的,Y在前,然后是U,最后是V。

把4:2:2格式转换成4:2:O格式,要保留所有的Y,并取第0,2,4,……行的U和第1,3,5……行的V。采用基于描述符列表“大”模式的MDMA,需要三对描述符source_y,dest_y,SOurce_u,dest_u,SOUrce_v,dest_v,形成源和目的两个描述符链表,进行Y,U和V的从交织的4:2:2格式的源数据区到Y,U和V分离的目的数据区的搬移。

当一帧CIF 4:2:2格式数据通过PPI填充到一个Blackfin处理器的视频帧缓冲区中,产生中断,在中断处理子程序中启动MDMA,分离亮度值和色度值,然后交给H.264编码器进行编码。

2.3 H.264编码

等待产生一帧4:2:O格式数据后,对这一帧数据执行H.264编码,之后继续等待4:2:0格式数据的产生,直至编码结束。

3 实验结果与分析

实验中,H.264编码器对摄像头采集到的图像编码,并将压缩码流以文件的形式保存在本地存储器中。编码结束后,用H.264的解码器对压缩码流解码,用YUVviewerPlus.exe播放解码后的视频文件。

实验中,编码器可达到每秒钟编码15帧图像的速度。解码后的图像清晰度与在VisualDsp++5.0中用Image Viewer查看的相比,图像质量基本相同,图像很清晰。OV7660采集图像的速度是每秒钟30帧,H.264编码器没有达到实时编码。

实验中,基于BF561的H.264编码器没有达到实时编码的原因是没有对H.264开源代码优化。由于CIF格式图像数据比较大,需要存储在外部存储器中,处理器访问外部存储器时间比较长;DCT和运动估计算法函数比较耗时,用C语言实现;程序中有一些辅助函数和打印信息等,从而影响了编码器的速度口。

4 结 语

基于BF561的H.264编码器没有达到实时编码。未来的工作重点是利用VisualDSP++开发环境的C编译器,进行代码优化;充分利用内部存储空间资源和尽可能通过DMA、高速缓存等减少存储分配带来的片内外数据调度对系统性能的影响;对一些系统调用比较频繁、耗时较多的模块,如DCT和运动估计等,充分利用BF561的指令集,用汇编语言实现;去掉源程序中不必要的辅助函数和打印信息,以实现基于BF561的H.264编码器实时编码。

随着消费类电子产品进一步进入普通家庭,应用H.264标准的视频会议、可视电话以及无人监控系统等也将会得到越来越广泛的应用。