基于TMS320C6416T的数据采集存储系统设计

Design of data acquisition and storage system based on TMS320C6416TAbstract: The analog-to-digital converter is an important precondition and pivotal tache of digital signal processing.In this paper,a data acquisition and stroage system based on high performance DSP TMS320C6416T and ADC THS12082 are provided.The experiment indicates that the high speed data acquisition and storage system has high speed DSP characteristics. It can be applied in many fields, for example, radar, communications, control, automotive and so on.

Keywords: analog-to-digital converter; sampling system; memory; data/digital signal processor; TMS320C6416T; THS12082

摘要: 模数转换是数字信号处理的重要前提和关键环节,设计了基于TMS320C6416T型DSP和THS12082型A/D转换器的数据采集存储系统。实验表明,该高速数据采集存储系统具有高速的DSP特性,可广泛应用于雷达、通信、控制、自动化等领域。

关键词: 模数转换器; 采样系统; 存储器; 数据/数字信号处理器; TMS320C6416T; THS12082

随着数字信号处理技术的飞速发展,模数转换作为数字信号处理的前端,其重要作用日益凸显。采用DSP器件TMS320C6416T,结合A/D转换器THS12082和SDRAMHY57V283220T实现高速通用数据采集存储系统,该系统可为数字信号处理提供数字化前端,充分发挥高性能DSP在数字信号处理上的优势,广泛应用于雷达、通信等领域。

2 器件简介

2.1 TMS320C6416T简介

TMS320C6416T型DSP工作主频高达1 GHz,处理性能可达8 000 MI/s,片上存储器采用两级存储器结构,第一级存储器包括相互独立的程序和数据,只能用于CPU高速缓存访问;第二级存储器寻址空间为1 M字节,可以选择配置为SRAM或2级Cache。片内资源主要含有增强型直接存储器访问(EDMA)控制器、外部存储器接口(EMIF)、主机接口(HPI)、通用目标输入输出(GPIO)、多通道缓冲串行接口(McBSP)、中断选择器、定时器、节电逻辑等。

2.2 THS12082简介

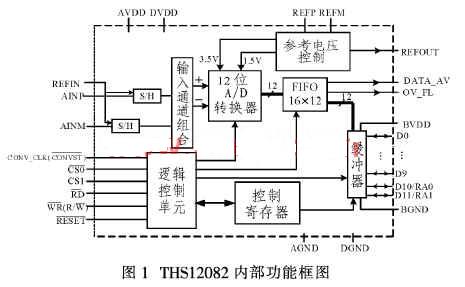

THS12082是TI公司的可编程、双通道、低功耗、内置FIFO的8MS/s采样速率的12位并行高速A/D转换器,可与DSP实现无缝链接。THS12082含有两路采样保持器,可同时对两路信号采样保持,并按顺序转换各通道的采样保持值。单通道最高采样频率可达8 MS/s。而同时采样两通道的模拟信号,其采样频率为4 MS/s。THS12082内部功能框图如图1所示。

3 系统硬件设计

3.1 数据采集电路设计

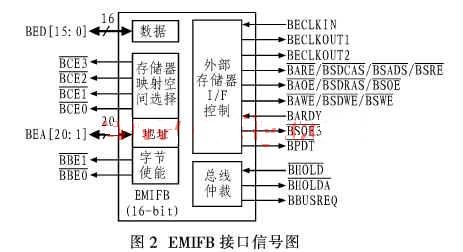

TMS320C6416T的外部存储器接口(EMIFA、EMIFB)可与外部元件无缝链接,片外设备(存储器或I/O)则通过外部存储器接口(EMIF)进行访问。其中EMIFB为16位存储器总线,分成4个空间.即BCE0~BCE3,每个存储空间可独立配置。本系统设计采用EMIFB的BCE2存储空间,最高工作频率为133 MHz,工作时钟来源为BECLKIN(外部输入时钟)、CPU时钟四分频(250 MHz)、CPU时钟六分频(167 MHz)。EMIFB接口信号如图2所示,其中BECLKOUT1时钟输出和EMIFB输入时钟的频率相同。BECLKOUT2输出时钟的频率为EMIFB输入时钟频率的1/2或/14。BED[15:0]为16位数据总线,BEA[20:1]为20位外部地址总线。

相关推荐

为铁路谐波干扰的研究搭建一个数据采集和监控系统

数据采集

2011-07-25

在线研讨会

焦点