基于XCR3256的低功耗存储测试器设计

正如我们所知,对于可编程逻辑器件,其内部触发器的翻转次数以及开关量的输出对器件本身的功耗影响非常大。该设计通过软件实现了主控芯片自身的功耗调节,通过控制系统内芯片使能以及总线的工作状态实现了系统级的低功耗。

在主程序中采用状态机编码,对输入输出信号进行赋值保护。对最终输出信号不需要更新的输入信号利用状态机控制阻止其传播至下一个状态或其他逻辑块。仅在需要时改变输出值,减少了不必要的开关输出。

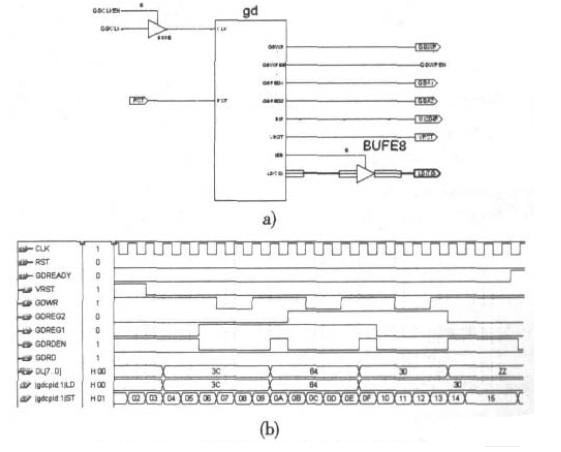

图5

从数据采集处理模块出来进入数据存储模块的数据其实为三路数据,通过状态机利用锁存器使三路数据在不同时刻占用存储器的数据总线,有效抑制了无效的开关活动。

在整个系统的工作过程中,有时候一些器件的行为对当前的功能实现不是必须的,但增加了多余功耗。如存储器的功耗在片选有效时,无论读写信号状态如何,都将比片选无效时大几十倍以上。在该系统中通过把一个控制系统映射到中心控制模块,在满足必要约束的条件下,尽可能的缩短了各芯片和控制逻辑的片选及使能。通过解除与当前操作无关的器件的使用,有效地减少了系统的总开关活动,降低了系统的功耗。

在整个程序中分为消抖模块、

图5(a)中

此外,系统时钟频率越高,时钟信号开关活动越频繁,电容性负载就越大,系统功耗也就越大。因此,系统时钟对系统功耗也有显著的影响。结合实际情况,在该设计中选用9. 8306MHz的晶振。

3 结束语

该数据存储测试器技术指标如下:

◆数据存储容量2MByte;

◆数据存储波道30路;

◆80路模拟量采样;

◆422差分串行数字量采样;

◆并行数字量采集;

◆系统功耗:50mA;

相关技术已应用于某某项目的测试,在运动过程中对系统的数字量和模拟量进行存储和重发,取得了良好的效果。

该技术的应用已扩展到各个领域,不仅可为飞行器的重要参数的获取提供了经济、高效的手段,也可为飞机、汽车、坦克、船舶、潜艇等地面、水上、水下运载工具的故障分析提供了充分的依据,对不断完善各类运载工具,降低其研制、维修成本具有一定的意义。