# TPS2359 Full Featured Dual-Slot AdvancedMC<sup>™</sup> Controller

## FEATURES

- ATCA AdvancedMC<sup>™</sup> Compliant

- Full Control for Two AdvancedMC<sup>™</sup> Modules

- Independent 12-V Current Limit and Fast Trip

- 3.3-V and 12-V FET ORing for MicroTCA™

- Internal 3.3-V Current Limit and ORing

- Power Good and Fault Reporting Through I<sup>2</sup>C

- I<sup>2</sup>C Programmable Fault Times and Current Limits

- FET Status Bits for all Channels

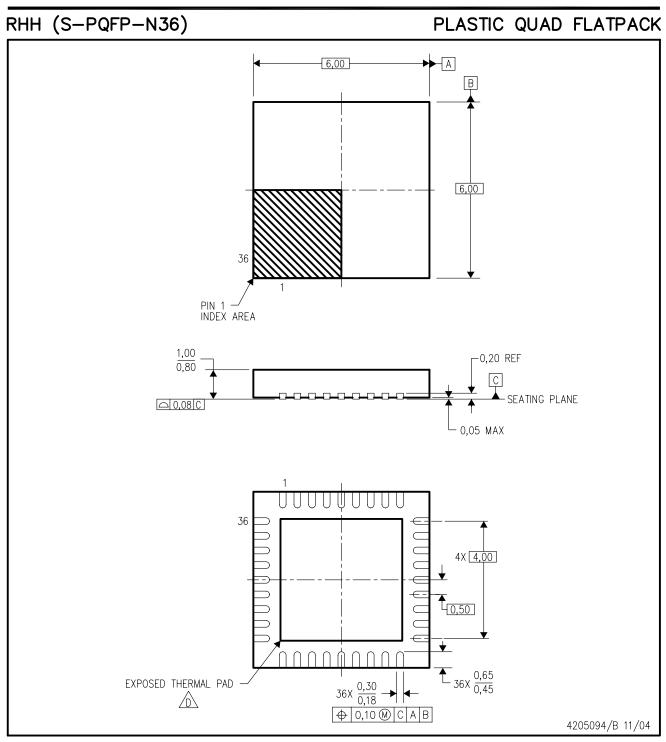

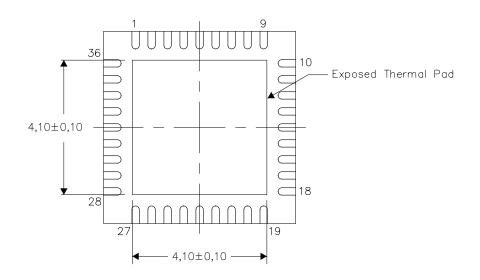

- 36-Pin PQFN Package

# **APPLICATIONS**

- ATCA Carrier Boards

- MicroTCA<sup>™</sup> Power Modules

- AdvancedMC<sup>™</sup> Slots

- Systems Using 12 V and 3.3 V

- Base Stations

# DESCRIPTION

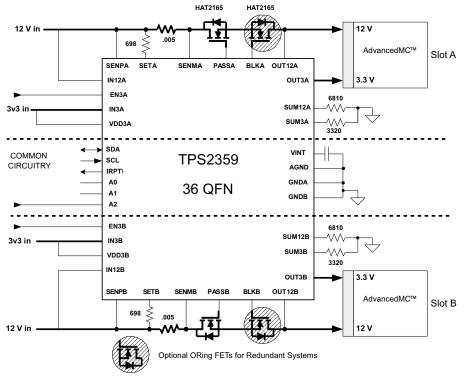

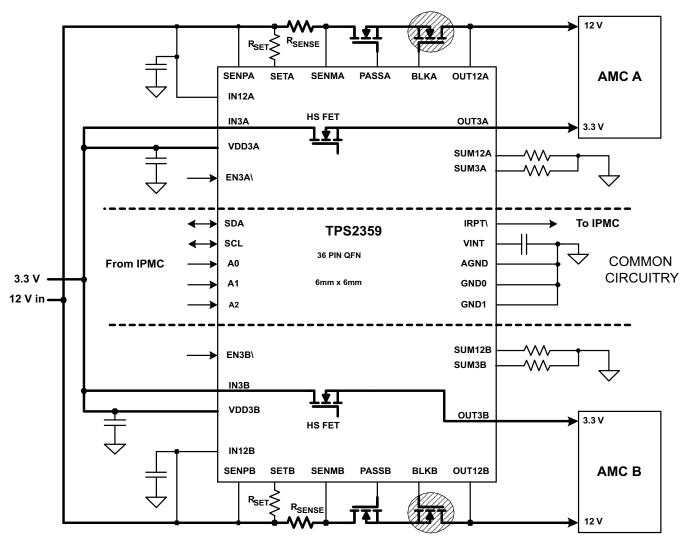

The TPS2359 dual-slot hot-plug controllers perform all necessary power interface functions for two AdvancedMC<sup>™</sup> (Advanced Mezzanine Card) modules.

Two fully integrated 3.3-V channels provide inrush control, over-current protection, and FET ORing. Two 12-V channels provide the same functions using external FETs and sense resistors. The 3.3-V current limits are factory set to AdvancedMC<sup>TM</sup> compliant levels and the 12-V current limits are programmed using external sense resistors. The accurate current sense comparators of the TPS2359 satisfy the narrow ATCA<sup>TM</sup> AdvancedMC<sup>TM</sup> current limit requirements.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. AdvancedMC, MicroTCA are trademarks of PICMG.

# TPS2359 Application Diagram

www.ti.com

#### ORDERING INFORMATION <sup>(1)</sup>

| DEVICE  |               |       | ORDERING INFORMATION |

|---------|---------------|-------|----------------------|

| TPS2359 | -40°C to 85°C | QFN36 | TPS2359RHH           |

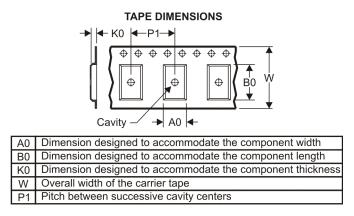

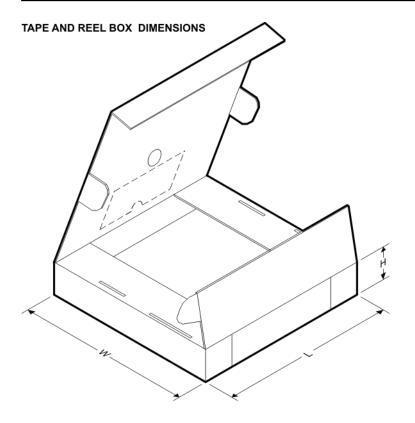

(1) Add an R suffix to the device type for tape and reel.

(2) For the most current package and ordering information see the Package Option Addendum at the end of this document or see the TI Web site at www.ti.com.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                               | VALUE              | UNIT |

|-----------------------------------------|--------------------|------|

| PASSx, BLKx                             | 0 to 30            |      |

| IN12x; OUT12x; SENPx; SENMx; SETx; IRPT | 0 to 17            |      |

| IN3x; OUT3x; EN3x; VDDx; SUMx; SDA, SCL | 0 to 5             | V    |

| AGND, GNDx                              | -0.3 to 0.3        |      |

| A0, A1, A2                              | 0 to VINT          | _    |

| SUMx                                    | 5                  |      |

| VINT                                    | -1 to 1            | mA   |

| OUT3x                                   | Internally limited |      |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device under any conditions beyond those indicated under recommended operating conditions is neither implied nor guaranteed. Exposure to absolute maximum rated conditions for extended periods of time may affect device reliability.

### **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

| TEST METHOD                | MIN | UNITS |

|----------------------------|-----|-------|

| Human Body Model (HBM)     | 2   | k)/   |

| Charged Device model (CDM) | 0.5 | kV    |

### **DISSIPATION RATINGS**

| PACKAGE | θJA - High-k (°C/W) |

|---------|---------------------|

| 36 QFN  | 35                  |

### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                            | MIN | ТҮР | MAX  | UNIT |

|----------------------|--------------------------------------|-----|-----|------|------|

| V <sub>IN12x</sub>   | Payload power input voltage          | 8.5 | 12  | 15   |      |

| V <sub>IN3x</sub>    | Management power input voltage       | 3   | 3.3 | 4    | V    |

| V <sub>VDD3x,3</sub> | Management power supply voltage      | 3   | 3.3 | 4    |      |

| I <sub>OUT3x</sub>   | Management power output current      |     |     | 165  | mA   |

| I <sub>SUMx</sub>    | Summing pin current                  |     | 100 | 1000 | ۵    |

|                      | PASSx pin board leakage current      | -1  |     | 1    | μΑ   |

|                      | VINT bypass capacitance              | 1   | 10  | 250  | nF   |

| TJ                   | Operating junction temperature range | -40 |     | 125  | °C   |

www.ti.com

## ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

IN3A = IN3B = VDD3A = VDD3B = 3.3 V. IN12A = IN12B = SENPA = SENPB = SENMA = SENMB = SETPA = SETPB = 12 V. EN3A = EN3B = AGND = GNDA = GNDB = 0 V. SUM12A = SUM12B = 6.8 k $\Omega$  to ground. SUM3A = SUM3B = 3.3 k $\Omega$  to ground. All other pins open. All I2C bits at default values. Over free air temperature operating range and all voltages referenced to AGND, unless otherwise noted. over operating free-air temperature range (unless otherwise noted)

| PARAMETER                          | CONDITIONS                                                                                                                                          | MIN  | TYP   | MAX  | UNITS |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--|

| ENABLE Inputs                      |                                                                                                                                                     |      |       |      |       |  |

| Threshold voltage, falling edge    |                                                                                                                                                     | 1.2  | 1.3   | 1.4  | V     |  |

| Hysteresis <sup>(2)</sup>          |                                                                                                                                                     | 20   | 50    | 80   | mV    |  |

| Pullup current2                    | EN3x = 0 V                                                                                                                                          |      | 8     | 15   | A     |  |

| Input bias current                 | EN3x = 5 V                                                                                                                                          |      | 1     | 5    | μA    |  |

| 3.3-V turn off time                | EN3x deasserts to $V_{OUT3x}$ < 1.0 V, $C_{OUT}$ = 0 $\mu$ F                                                                                        |      |       | 10   |       |  |

| 12-V turn off time                 |                                                                                                                                                     |      | 20    | μs   |       |  |

| VINT                               |                                                                                                                                                     |      |       |      |       |  |

| Output voltage                     | 0 < I <sub>VINT</sub> < 50 μA                                                                                                                       | 2    | 2.3   | 2.8  | V     |  |

| Power GOOD Comparators             |                                                                                                                                                     |      |       |      |       |  |

| Thursele and such a se             | 12xPG, falling OUT12x                                                                                                                               | 10.2 | 10.5  | 10.8 | N/    |  |

| Threshold voltage                  | 3xPG, falling OUT3x                                                                                                                                 | 2.7  | 2.8   | 2.9  | V     |  |

| Hystorosis                         | 12xPG, measured at OUT12x                                                                                                                           |      | 130   |      | mV    |  |

| Hysteresis                         | 3xPG, measured at OUT3x                                                                                                                             |      | 50    |      |       |  |

| Fault Timer                        |                                                                                                                                                     |      |       |      |       |  |

| Minimum fault time                 | 3xFT[4:0] = 12xFT[4:0] = 00001B                                                                                                                     |      | 1     |      |       |  |

| Fault time bit weight              |                                                                                                                                                     |      | 0.5   |      | ms    |  |

| Timer duty cycle                   | = (fault time) / (retry period)                                                                                                                     | 1.4% | 1.5%  | 1.6% |       |  |

| 12-V Summing node                  |                                                                                                                                                     |      |       |      |       |  |

| Input referred offset              | $\label{eq:V_SENMx} \begin{array}{l} V_{SENMx} = 10.8 - 13.2 \ V, \ V_{SENPx} = V_{SENMx} + 50 \\ mV, \ measure \ V_{SETx} - V_{SENMx} \end{array}$ | -2   |       | 2    | mV    |  |

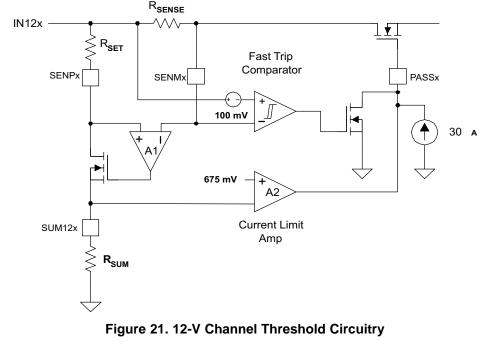

| Summing threshold                  | 12xCL[3:0] = 1111B, VPASSx = 15 V                                                                                                                   | 0.66 | 0.675 | 0.69 | V     |  |

| Leakage current                    | VSETx = VSENMx - 10 mV                                                                                                                              |      |       | 1    | μΑ    |  |

| 12-V Current limit                 |                                                                                                                                                     |      |       |      |       |  |

| Current limit threshold            | $R_{SUMx}$ = 6.8 kΩ, $R_{SETx}$ = 422 Ω, increase $I_{LOADx}$ and measure $V_{SENPx}$ – $V_{SENMx}$ when $V_{PASSx}$ = 15 V                         |      | 50    | 52.5 | mV    |  |

| Sink current in current limit      | $V_{SUMx}$ = 1 V, $V_{PASSx}$ = 12 V, measure $I_{PASSx}$                                                                                           | 20   |       | 40   | μΑ    |  |

| Fast trip threshold                | Measure V <sub>SENPx</sub> – V <sub>SENMx</sub>                                                                                                     | 80   | 100   | 120  | mV    |  |

| Fast turn-off delay <sup>(2)</sup> | 20-mV overdrive, $C_{PASSx} = 0 \text{ pF}$ , $t_{p50-50}$                                                                                          |      | 200   | 300  | ns    |  |

| Bleed down resistance              | V <sub>OUT</sub> = 6 V                                                                                                                              | 1.1  | 1.6   | 2.1  | kΩ    |  |

| Bleed down threshold               |                                                                                                                                                     | 75   | 100   | 130  | mV    |  |

| Timer start threshold              | $V_{PASSx} - V_{INx}$ when fault timer starts                                                                                                       | 5    | 6     | 7    | V     |  |

(1) When setting an address bit to a logic 1 the pin should be connected to VINT.

(2) Not production tested.

www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

IN3A = IN3B = VDD3A = VDD3B = 3.3 V. IN12A = IN12B = SENPA = SENPB = SENMA = SENMB = SETPA = SETPB = 12 V. EN3A = EN3B = AGND = GNDA = GNDB = 0 V. SUM12A = SUM12B =  $6.8 \text{ k}\Omega$  to ground. SUM3A = SUM3B =  $3.3 \text{ k}\Omega$  to ground. All other pins open. All I2C bits at default values. Over free air temperature operating range and all voltages referenced to AGND, unless otherwise noted. over operating free-air temperature range (unless otherwise noted)

| PARAMETER                            | PARAMETER CONDITIONS                                                                                                                                                                                        |      | TYP  | MAX  | UNITS |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| 12-V UVLO                            |                                                                                                                                                                                                             | L.   |      |      |       |

| UVLO rising                          | IN12x rising                                                                                                                                                                                                | 8.1  | 8.5  | 8.9  |       |

| UVLO hysteresis                      | IN12x falling                                                                                                                                                                                               | 0.44 | 0.5  | 0.59 | V     |

| 12-V BLOCKING                        | <u>_</u>                                                                                                                                                                                                    |      |      |      |       |

| Turn-on threshold                    | Measure V <sub>SENPx</sub> – V <sub>OUTx</sub>                                                                                                                                                              | 5    | 10   | 15   |       |

| Turn-off threshold                   | Measure V <sub>SENPx</sub> – V <sub>OUTx</sub>                                                                                                                                                              | -5   | -3   | 0    | mV    |

| Turn-off delay <sup>(3)</sup>        | 20-mV overdrive, $C_{BLKx} = 0 \text{ pF}$ , $t_{p50-50}$                                                                                                                                                   |      | 200  | 300  | ns    |

| 12-V Gate drivers (PASSx, BL         |                                                                                                                                                                                                             |      |      |      |       |

| Output voltage                       | $V_{INx} = V_{OUTx} = 10 V$                                                                                                                                                                                 | 21.5 | 23   | 24.5 | V     |

| Sourcing current                     | V <sub>IN12x</sub> = V <sub>OUT12x</sub> = 10 V, V <sub>PASSx</sub> = V <sub>BLKx</sub> = 17 V                                                                                                              | 20   | 30   | 40   | μΑ    |

| Cializa coment                       | Fast turnoff, V <sub>PASSx</sub> = V <sub>BLKx</sub> = 14 V                                                                                                                                                 | 0.5  | 1    |      | А     |

| Sinking current                      | Sustained, $V_{PASSx} = V_{BLKx} = 4 - 25 V$                                                                                                                                                                | 6    | 14   | 25   | mA    |

| Pulldown resistance                  | In OTSD (at 150 °C)                                                                                                                                                                                         | 14   | 20   | 26   | kΩ    |

| Fast turnoff duration <sup>(3)</sup> |                                                                                                                                                                                                             | 5    | 10   | 15   | ms    |

| Safety gate pulldown <sup>(3)</sup>  | IRF3710, slew S or D 15 V in 1 ms                                                                                                                                                                           |      |      | 1.25 | V     |

| Startup time <sup>(3)</sup>          |                                                                                                                                                                                                             |      | 0.25 | ms   |       |

| 3.3-V Summing node                   |                                                                                                                                                                                                             | L.   |      |      |       |

| Summing threshold                    |                                                                                                                                                                                                             | 655  | 675  | 695  | mV    |

| 3.3-V Current limit                  | <u>_</u>                                                                                                                                                                                                    |      |      |      |       |

| On resistance                        | I <sub>OUT3x</sub> = 150 mA                                                                                                                                                                                 |      | 290  | 500  | mΩ    |

| Current limit                        | $R_{SUM3x} = 3.3 \text{ k}\Omega$ , $V_{OUT3x} = 0 \text{ V}$                                                                                                                                               | 170  | 195  | 225  |       |

| Fast trip threshold                  |                                                                                                                                                                                                             | 240  | 300  | 400  | mA    |

| Fast turn-off delay <sup>(3)</sup>   | I <sub>OUT3x</sub> = 400 mA, t <sub>p50-50</sub>                                                                                                                                                            |      | 750  | 1300 | ns    |

| Bleed down resistance                | V <sub>OUT3x</sub> = 1.65 V                                                                                                                                                                                 | 280  | 400  | 500  | Ω     |

| Bleed down threshold                 |                                                                                                                                                                                                             | 75   | 100  | 130  | mV    |

| 3.3-V UVLO                           |                                                                                                                                                                                                             | L.   |      |      |       |

| UVLO rising                          | IN3x rising                                                                                                                                                                                                 | 2.65 | 2.75 | 2.85 | V     |

| UVLO hysteresis                      | IN3x falling                                                                                                                                                                                                | 200  | 240  | 300  | mV    |

| 3.3-V Blocking                       |                                                                                                                                                                                                             | L.   |      |      |       |

| Turn-on threshold                    | Measure V <sub>IN3x</sub> – V <sub>OUT3x</sub>                                                                                                                                                              | 5    | 10   | 15   |       |

| Turn-off threshold                   | Measure V <sub>IN3x</sub> – V <sub>OUT3x</sub>                                                                                                                                                              | -5   | -3   | 0    | mV    |

| ORing turn-on delay                  | $V_{IN3x} = 3.3 \text{ V}, V_{OUT3x} = 3.5 \text{ V}, OUT3x = 100 \Omega \text{ to}$<br>GND, 30RON = 1. Remove 3.5 V from OUT3x.<br>Measure time from $V_{OUT3x}$ thru 2.9 V to $V_{OUT3x} = 3.2 \text{ V}$ |      | 300  | 350  | μs    |

| Fast turnoff delay <sup>(3)</sup>    | 20 mV overdrive, t <sub>p50-50</sub>                                                                                                                                                                        |      | 250  | 350  | ns    |

(3) Not production tested.

www.ti.com

### **ELECTRICAL CHARACTERISTICS (continued)**

IN3A = IN3B = VDD3A = VDD3B = 3.3 V. IN12A = IN12B = SENPA = SENPB = SENMA = SENMB = SETPA = SETPB = 12 V. EN3A = EN3B = AGND = GNDA = GNDB = 0 V. SUM12A = SUM12B = 6.8 k $\Omega$  to ground. SUM3A = SUM3B = 3.3 k $\Omega$  to ground. All other pins open. All I2C bits at default values. Over free air temperature operating range and all voltages referenced to AGND, unless otherwise noted. over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                                 | CONDITIONS                                                | MIN        | TYP  | MAX  | UNITS |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------|------------|------|------|-------|--|

| Supply Currents (I <sub>INx</sub> + I <sub>SENPx</sub> + I <sub>SEN</sub> | IMx + I <sub>SETx</sub> + I <sub>VDDx</sub> )             | I          |      |      |       |  |

| All channels enabled                                                      | $I_{OUT3A} = I_{OUT3B} = 0$                               |            | 3.1  | 4    | ~ ^   |  |

| All channels disabled                                                     | I channels disabled                                       |            |      |      | mA    |  |

| Thermal Shutdown                                                          |                                                           | <b>i</b> i |      |      |       |  |

| Whole-chip shutdown temperature <sup>(4)</sup>                            | $T_J$ rising, $I_{OUT3A} = I_{OUT3B} = 0$                 | 140        | 150  |      |       |  |

| 3.3-V channel shutdown temperature <sup>(4)</sup>                         | $T_J$ rising, $I_{OUT3A}$ or $I_{OUT3B}$ in current limit | 130        | 140  |      | °C    |  |

| Hysteresis <sup>(4)</sup>                                                 |                                                           | 10         |      |      |       |  |

| Serial Interface (SDA, SCL, A0-2, IF                                      | RPT                                                       | I          |      |      |       |  |

| Lower logic threshold                                                     | A0 – A2                                                   | 0.33       | 0.35 | 0.37 | N/    |  |

| Upper logic threshold                                                     | A0 – A2                                                   | 1.32       | 1.35 | 1.38 | V 88  |  |

| Input pullup resistance                                                   | $A0 - A2$ , $V_{Ax} = 0$ V                                | 400        | 700  | 1000 | 1.0   |  |

| Input pulldown resistance                                                 | $A0 - A2$ , $V_{Ax} = VINT$                               | 200        | 350  | 550  | kΩ    |  |

| Input open-circuit voltage                                                | IAx = 0 V                                                 | 0.5        | 0.8  | 1.0  |       |  |

| Threshold voltage, rising                                                 | SDA, SCL                                                  |            |      | 2.3  | V     |  |

| Threshold voltage, falling                                                | SDA, SCL                                                  | 1.0        |      |      |       |  |

| Hysteresis <sup>(4)</sup>                                                 | SDA, SCL                                                  | 165        |      |      | mV    |  |

| Leakage                                                                   | SDA, IRPT                                                 |            |      | 1    | mA    |  |

| Input clock frequency                                                     | SCL                                                       |            |      | 400  | kHz   |  |

(4) Not production tested.

### Signal and Pin Naming Convention

#### SIGNAL AND PIN NAMING

The PICMG<sup>™</sup> AdvancedMC<sup>™</sup> specification refers to 3.3 V power as Management Power and refers to 12 V power as Payload Power. This datasheet uses a naming convention that reflects the associated voltage (12 or 3.3 V) and arbitrary AdvancedMC<sup>™</sup> slot (A or B).

- Signals and pins associated with slot A 12 V payload power end with 12A

- Signals and pins associated with slot A 3.3 V management power end with 3A

- Signals and pins associated with slot B 12 V payload power end with 12B

- Signals and pins associated with slot B 3.3 V management power end with 3B

Pins and signals unique to 12 V channels have only an A or B suffix.

The register names are similar except the voltage/slot identifier is at the beginning of the bit name.

www.ti.com

# DEVICE INFORMATION

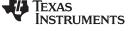

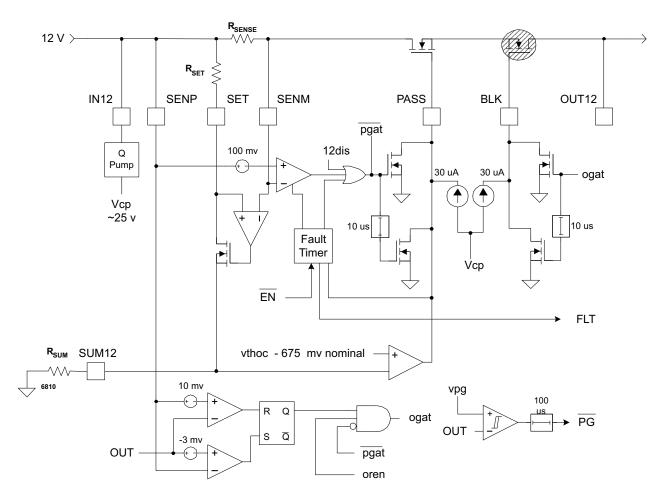

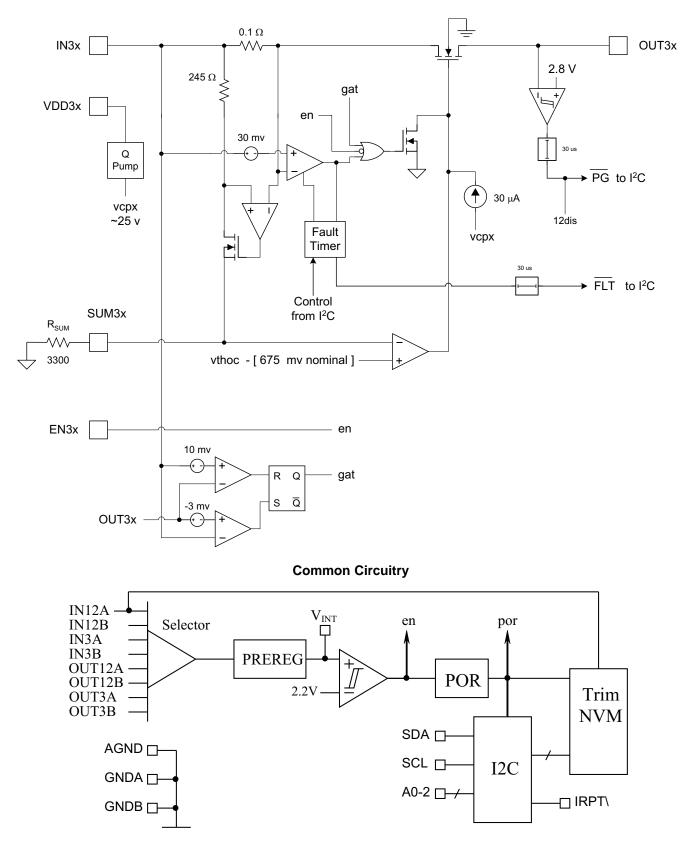

## **TPS2359 BLOCK DIAGRAMS**

Figure 1. Payload Power Channel (two channels per device)

Submit Documentation Feedback

#### SLUS792D-FEBRUARY 2008-REVISED JUNE 2008

Management Power Channel (two channels per device)

# **TPS2359**

TEXAS INSTRUMENTS

#### SLUS792D-FEBRUARY 2008-REVISED JUNE 2008

www.ti.com

# SLUS792D-FEBRUARY 2008-REVISED JUNE 2008

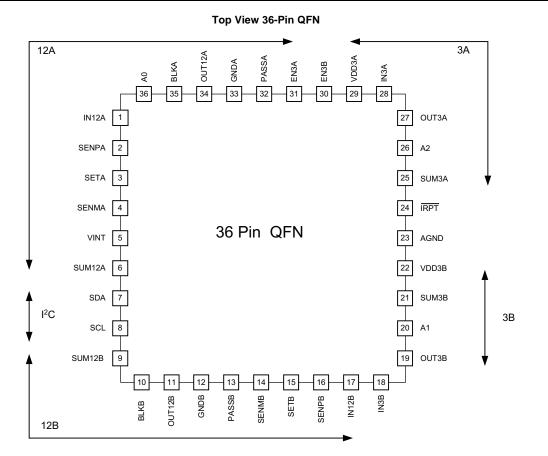

#### **TPS2359 TERMINAL FUNCTIONS**

| PIN # | NAME   | TYPE            | DESCRIPTION                                                               |

|-------|--------|-----------------|---------------------------------------------------------------------------|

| 1     | IN12A  | V <sub>DD</sub> | 12A input                                                                 |

| 2     | SENPA  | I               | 12A input sense                                                           |

| 3     | SETA   | I               | 12A current limit set                                                     |

| 4     | SENMA  | I               | 12A current limit sense                                                   |

| 5     | VINT   | I/O             | Bypass capacitor connection point for internal supply, pullup for A0 – A2 |

| 6     | SUM12A | I/O             | 12A summing node                                                          |

| 7     | SDA    | I/O             | Serial data input/output                                                  |

| 8     | SCL    | I               | Serial data clock                                                         |

| 9     | SUM12B | I/O             | 12B summing node                                                          |

| 10    | BLKB   | 0               | 12B blocking transistor gate drive                                        |

| 11    | OUT12B | I/O             | 12B output                                                                |

| 12    | GNDB   | GND             | 12B power ground                                                          |

| 13    | PASSB  | 0               | 12B pass transistor gate drive                                            |

| 14    | SENMB  | I               | 12B current limit sense                                                   |

| 15    | SETB   | I               | 12B current limit set                                                     |

| 16    | SENPB  | I               | 12B input sense                                                           |

| 17    | IN12B  | V <sub>DD</sub> | 12B input                                                                 |

| 18    | IN3B   | V <sub>DD</sub> | 3B input                                                                  |

| 19    | OUT3B  | I/O             | 3B output                                                                 |

| 20    | A1     | I               | I <sup>2</sup> C address programming bit, LSB+1                           |

| 21    | SUM3B  | I/O             | 3B summing node                                                           |

| 22    | VDD3B  | V <sub>DD</sub> | 3B charge pump input                                                      |

| 23    | AGND   | GND             | Analog ground                                                             |

| 24    | IRPT   | 0               | Active low interrupt, asserts when a PG deasserts or when a FLT\ asserts  |

| 25    | SUM3A  | I/O             | 3A summing node                                                           |

| 26    | A2     | l               | I <sup>2</sup> C address programming bit, LSB+2                           |

| 27    | OUT3A  | I/O             | 3A output                                                                 |

| 28    | IN3A   | V <sub>DD</sub> | 3A input                                                                  |

| 29    | VDD3A  | V <sub>DD</sub> | 3A charge pump input                                                      |

| 30    | EN3B   | I               | 3B enable, active high                                                    |

| 31    | EN3A   | l               | 3A enable, active high                                                    |

| 32    | PASSA  | 0               | 12A pass transistor gate drive                                            |

| 33    | GNDA   | GND             | 12A power ground                                                          |

| 34    | OUT12A | I/O             | 12A output                                                                |

| 35    | BLKA   | 0               | 12A blocking transistor gate drive                                        |

| 36    | A0     | I               | I <sup>2</sup> C address programming bit, LSB                             |

### DETAILED PIN DESCRIPTION

**A0, A1, A2** These three pins select one of 27 unique I<sup>2</sup>C addresses for address of the TPS2359. Each pin may be tied to ground, tied to the VINT pin, or left open. See TPS2359 I<sup>2</sup>C Interface section for details.

AGND Ground pin for analog circuitry inside the TPS2359.

**BLKx** Gate drive pin for the 12x channel BLK FET. This pin sources 30  $\mu$ A to turn the FET on. An internal clamp prevents this pin from rising more than 14.5 V above OUT12x. Setting the ORENx bit low holds the BLKx pin low.

**EN3x** Active-high enable input. Pulling this pin low turns off channel 3x by pulling the gate of the internal pass FET to GND. An internal 200-k $\Omega$  resistor pulls this pin up to VINTwhen disconnected.

**GNDx** Ground pin for power circuitry associated with the 12x channel. These pins should connect to a ground plane shared with the AGND pin.

**IN12x** Supply pin for channel 12x internal circuitry.

**IN3x** Supply pin for channel 3x internal pass FET.

**IRPT** Open drain output that pulls low when internal circuitry sets any of the eight status bits in Register 7. Reading Register 7 restores IRPT to its high-Z state.

**OUT12x** Senses the output voltage of the channel 12x path.

**OUT3x** Output of the channel 3x internal pass FET.

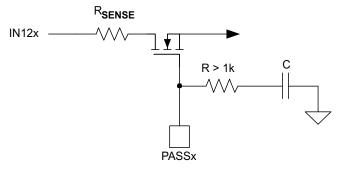

**PASSx** Gate drive pin for the 12x channel PASS FET. This pin sources 30 µA to turn the FET on. An internal clamps prevents this pin from rising more than 14.5 V above IN12x.

**SCL** Serial clock input for the I<sup>2</sup>C interface. For details of the SCL line, see TPS2359 I<sup>2</sup>C Interface section.

**SDA** Bidirectional I<sup>2</sup>C data line. For details of the SDA line, see TPS2359 I<sup>2</sup>C Interface section for details.

**SENMx** Senses the voltage on the low side of the channel 12x current sense resistor.

**SENPx** Senses the voltage on the high side of the channel 12x current sense resistor.

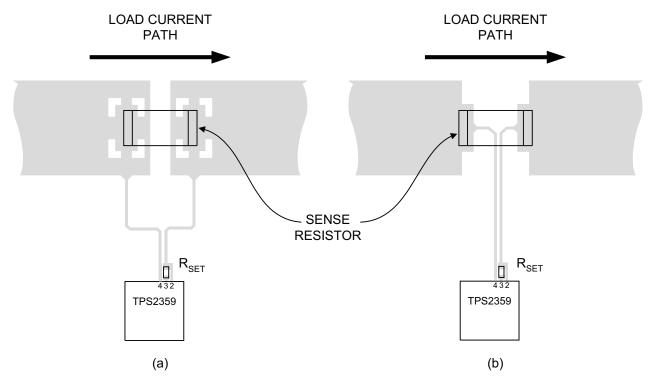

**SETx** A resistor connected from this pin to SENPx sets the current limit level in conjunction with the current sense resistor and the resistor connected to the SUM12x pin, as described in 12-V thresholds – setting current limit and fast over current trip section.

**SUMx** A resistor connected from this pin to ground forms part of the channel x current limit. As the current delivered to the load increases, so does the voltage on this pin. When the voltage on this pin reaches a threshold (by default 675 mV), the current limit amplifier acts to prevent the current from further increasing.

VDD3x Supply pin for channel3x internal circuitry.

**VINT** This pin connects to the internal 2.35-V rail. A  $0.1-\mu$ F capacitor must be connected from this pin to ground. One can connect the A0–A2 pins to this supply to pull them high, but no other external circuitry should connect to VINT.

TEXAS INSTRUMENTS

www.ti.com

SLUS792D-FEBRUARY 2008-REVISED JUNE 2008

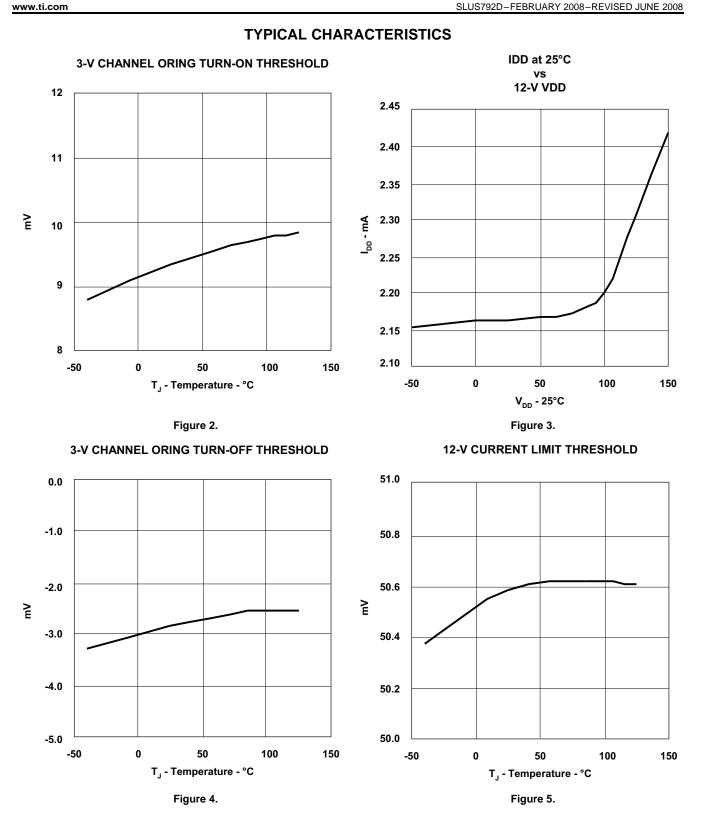

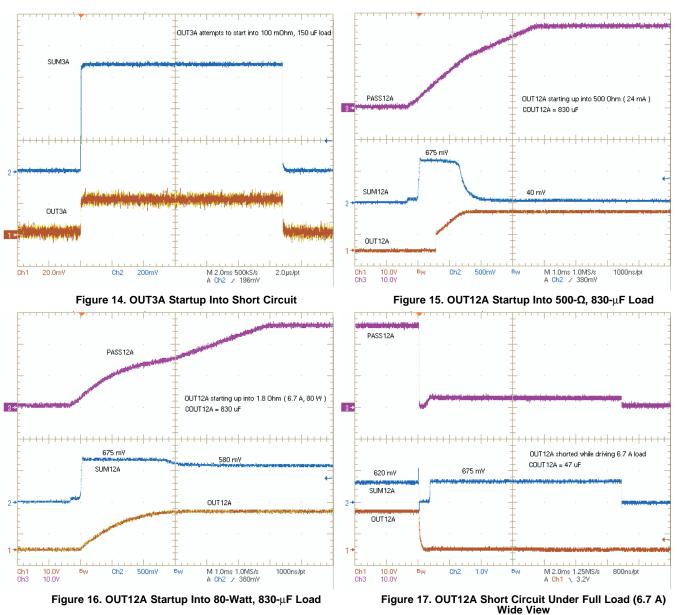

# **TYPICAL CHARACTERISTICS (continued)**

#### www.ti.com

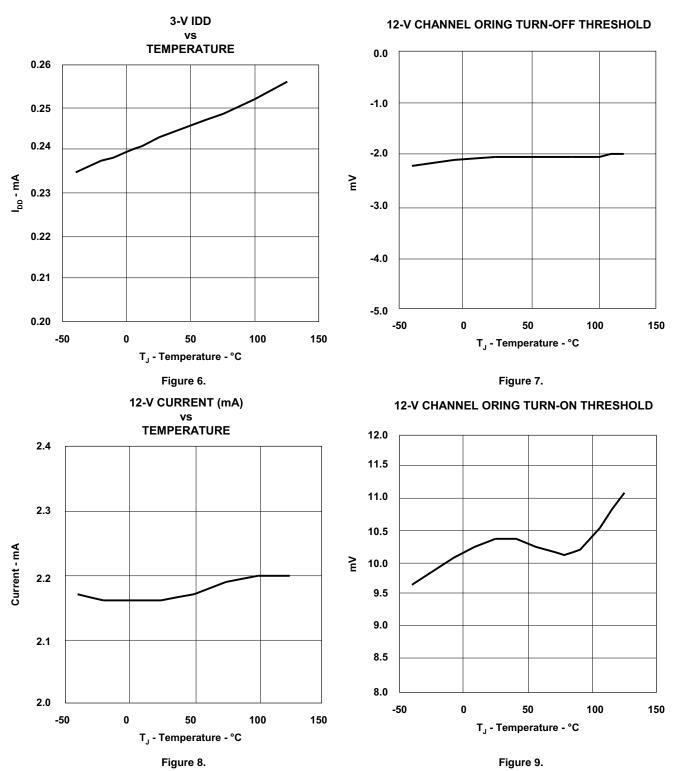

# TYPICAL CHARACTERISTICS (continued)

TEXAS INSTRUMENTS

www.ti.com

#### SLUS792D-FEBRUARY 2008-REVISED JUNE 2008

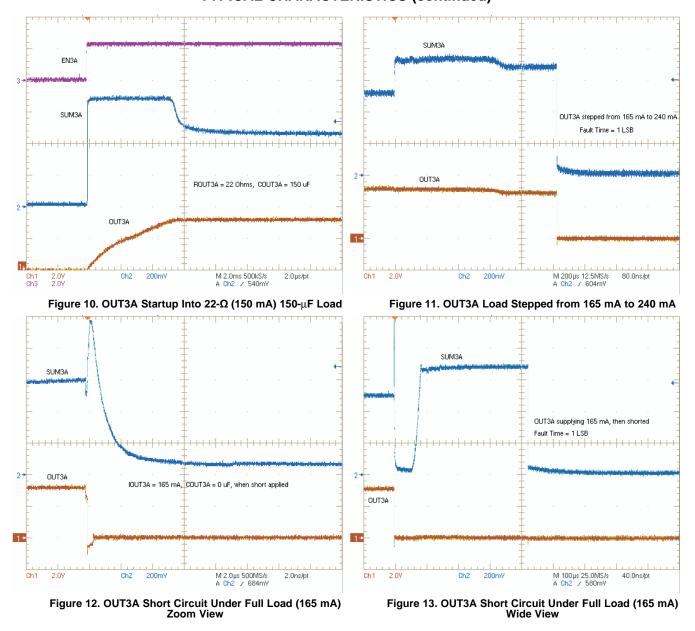

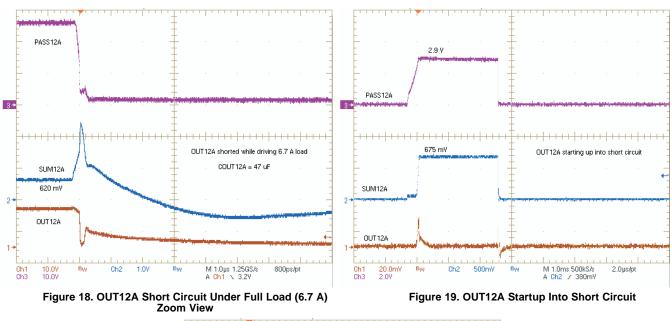

## **TYPICAL CHARACTERISTICS (continued)**

## Texas Instruments

#### SLUS792D-FEBRUARY 2008-REVISED JUNE 2008

## **TYPICAL CHARACTERISTICS (continued)**

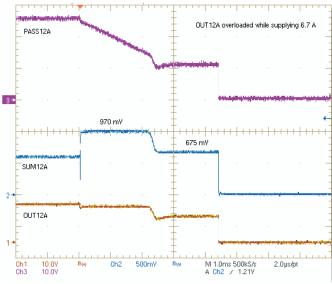

#### Figure 20. OUT12A Overloaded While Supplying 6.7 A

## **REFERENCE INFORMATION**

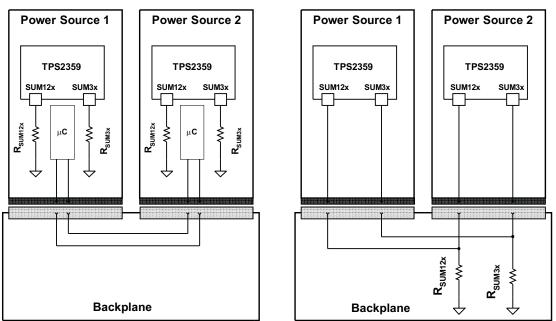

The TPS2359 has been designed to simplify compliance with the PICMG-AMC.R2.0 and PICMG-MTCA.0 specifications. These specifications were developed by the PCI Industrial Computer Manufacturers Group (PICMG). These two specifications are derivations of the PICMG-ATCA (Advanced Telecommunication Computing Architecture) specification originally released in December, 2002.

## **PICMG-AMC Highlights**

- AMC Advanced Mezzanine Cards

- Designed to Plug into ATCA Carrier Boards

- AdvancedMC<sup>™</sup> Focuses on Low Cost

- 1 to 8 AdvancedMC<sup>™</sup> per ATCA Carrier Board

- 3.3-V Management Power Maximum Current Draw of 150 mA

- 12-V Payload Power Converted to Required Voltages on AMC

- Maximum 80-W Dissipation per AdvancedMC<sup>™</sup>

- Hotswap and Current Limiting Must Be Present on Carrier Board

- For Details, see www.picmg.org/v2internal/AdvancedMC.htm

### **PICMG-MTCA Highlights**

- MTCA MicroTelecommunications Computing Architecture

- Architecture for Using AMCs Without an ATCA Carrier Board

- Up to 12 AMCs per System, Plus Two MCHs, Plus Two CUs

- Focuses on Low Cost

- All functions of ATCA Carrier Board Must Be Provided

- MicroTCA is also known as MTCA, mTCA, or uTCA For Details, see www.picmg.org/v2internal/microTCA.htm

### **Control and Status Registers**

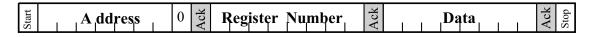

Ten 8 bit registers are used to control and read the status of the TPS2359. Registers 0 and 1 control the 12A channel and register 2 controls the 3A channel. Similarly, registers 3 and 4 control the 12B channel and register 5 controls the 3B channel. Register 6 contains eight general configuration bits. Read-only registers 7, 8, and 9 report back system status to the I<sup>2</sup>C controller. All ten registers use the I<sup>2</sup>C protocol and are organized as follows:

| REG | R/W | SLOT | VOLTAGE | FUNCTION                                                          |

|-----|-----|------|---------|-------------------------------------------------------------------|

| 0   | R/W | A    | 12      | Set current limit, power good threshold, and OR functions of 12A. |

| 1   | R/W | А    | 12      | Set fault time, enable, and bleed down functions of 12A.          |

| 2   | R/W | А    | 3.3     | Set fault time, enable, and bleed down functions of 3A.           |

| 3   | R/W | В    | 12      | Set current limit, power good threshold, and OR functions of 12B. |

| 4   | R/W | В    | 12      | Set fault time, enable, and bleed down functions of 12B.          |

| 5   | R/W | В    | 3.3     | Set fault time, enable, and bleed down functions of 3B.           |

| 6   | R/W | A, B | 3.3, 12 | System configuration controls.                                    |

| 7   | R   | A, B | 3.3, 12 | Fault and PG outputs for 3A, 12A, 3B, 12B – these bits set IRPT.  |

| 8   | R   | A, B | 12      | Over current and fast trip latches for 3A, 12A, 3B, 12B.          |

| 9   | R   | A, B | 3.3, 12 | Channel status indicators for 3A, 12A, 3B, 12B.                   |

#### Table 1. Top Level Register Functions

TPS2359

www.ti.com

# **Summary of Registers**

| BIT            | NAME               | DEFAULT         | DESCRIPTION                                                         |

|----------------|--------------------|-----------------|---------------------------------------------------------------------|

| Register 0 Rea | d/Write channel 12 | A configuration |                                                                     |

| 0              | 12ACL0             | 1               | Clearing bit reduces 12A current limit & fast threshold by 5%.      |

| 1              | 12ACL1             | 1               | Clearing bit reduces 12A current limit & fast threshold by 10%.     |

| 2              | 12ACL2             | 1               | Clearing bit reduces 12A current limit & fast threshold by 20%.     |

| 3              | 12ACL3             | 1               | Clearing bit reduces 12A current limit & fast threshold by 40%.     |

| 4              | 12APG0             | 1               | Clearing bit reduces 12A power good threshold by 600mV.             |

| 5              | 12APG1             | 1               | Clearing bit reduces 12A power good threshold by 1.2 V.             |

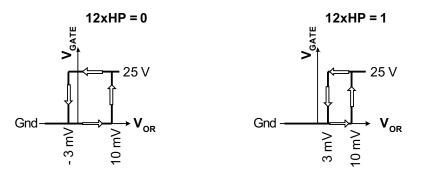

| 6              | 12AHP              | 0               | Setting bit shifts 12A OR VTURNOFF from –3 mV to +3 mV nominal.     |

| 7              | 12AOR              | 1               | Clearing bit turns off 12A ORing FET by pulling BLKA low.           |

| Register 1 Rea | d/Write channel 12 | A configuration |                                                                     |

| 0              | 12AFT0             | 1               | Setting bit increases 12A fault time by 0.5 ms.                     |

| 1              | 12AFT1             | 0               | Setting bit increases 12A fault time by 1 ms.                       |

| 2              | 12AFT2             | 0               | Setting bit increases 12A fault time by 2 ms.                       |

| 3              | 12AFT3             | 0               | Setting bit increases 12A fault time by 4 ms.                       |

| 4              | 12AFT4             | 0               | Setting bit increases 12A fault time by 8 ms.                       |

| 5              | 12AEN              | 0               | Clearing bit disables 12A by pulling PASSA and BLKA to 0 V.         |

| 6              | 12AUV              | 0               | Setting bit prevents enabling unless OUT12A < bleed down threshold. |

| 7              | 12ADS              | 0               | Clearing bit disconnects OUT12A bleed down resistor.                |

| Register 2 Rea | d/Write channel 3/ | A configuration |                                                                     |

| 0              | 3AFT0              | 1               | Setting bit increases 3A fault time by 0.5 ms.                      |

| 1              | 3AFT1              | 0               | Setting bit increases 3A fault time by 1 ms.                        |

| 2              | 3AFT2              | 0               | Setting bit increases 3A fault time by 2 ms.                        |

| 3              | 3AFT3              | 0               | Setting bit increases 3A fault time by 4 ms.                        |

| 4              | 3AFT4              | 0               | Setting bit increases 3A fault time by 8 ms.                        |

| 5              | 3AEN               | 0               | Clearing bit disables 3A.                                           |

| 6              | 3AUV               | 0               | Setting bit prevents enabling unless OUT3A < bleed down threshold.  |

| 7              | 3ADS               | 0               | Clearing bit disconnects OUT3A bleed down resistor.                 |

| Register 3 Rea | d/Write channel 12 | B configuration |                                                                     |

| 0              | 12BCL0             | 1               | Clearing bit reduces 12B current limit & fast threshold by 5%.      |

| 1              | 12BCL1             | 1               | Clearing bit reduces 12B current limit & fast threshold by 10%.     |

| 2              | 12BCL2             | 1               | Clearing bit reduces 12B current limit & fast threshold by 20%.     |

| 3              | 12BCL3             | 1               | Clearing bit reduces 12B current limit & fast threshold by 40%.     |

| 4              | 12BPG0             | 1               | Clearing bit reduces 12B power good threshold by 600 mV.            |

| 5              | 12BPG1             | 1               | Clearing bit reduces 12B power good threshold by 1.2 V.             |

| 6              | 12BHP              | 0               | Setting bit shifts 12B OR VTURNOFF from –3 mV to +3 mV nominal.     |

| 7              | 12BOR              | 1               | Clearing bit turns off 12B ORing FET by pulling BLKB low.           |

| Register 4 Rea | d/Write channel 12 | B configuration |                                                                     |

| 0              | 12BFT0             | 1               | Setting bit increases 12B fault time by 0.5 ms.                     |

| 1              | 12BFT1             | 0               | Setting bit increases 12B fault time by 1 ms.                       |

| 2              | 12BFT2             | 0               | Setting bit increases 12B fault time by 2 ms.                       |

| 3              | 12BFT3             | 0               | Setting bit increases 12B fault time by 4 ms.                       |

| 4              | 12BFT4             | 0               | Setting bit increases 12B fault time by 8 ms.                       |

| 5              | 12BEN              | 0               | Clearing bit disables 12B by pulling PASSB and BLKB to 0 V.         |

| 6              | 12BUV              | 0               | Setting bit prevents enabling unless OUT12B < bleed down threshold. |

| 7              | 12BDS              | 0               | Clearing bit disconnects OUT12B bleed down resistor.                |

# Table 2. Summary of Registers

Copyright © 2008, Texas Instruments Incorporated

www.ti.com

| Table 2. Su | ummary of | Registers | (continued) |

|-------------|-----------|-----------|-------------|

|-------------|-----------|-----------|-------------|

| BIT            | NAME               | DEFAULT          | DESCRIPTION                                                                                                                          |

|----------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Register 5 Rea | d/Write channel 3I | B configuration  |                                                                                                                                      |

| 0              | 3BFT0              | 1                | Setting bit increases 3B fault time by 0.5 ms.                                                                                       |

| 1              | 3BFT1              | 0                | Setting bit increases 3B fault time by 1 ms.                                                                                         |

| 2              | 3BFT2              | 0                | Setting bit increases 3B fault time by 2 ms.                                                                                         |

| 3              | 3BFT3              | 0                | Setting bit increases 3B fault time by 4 ms.                                                                                         |

| 4              | 3BFT4              | 0                | Setting bit increases 3B fault time by 8 ms.                                                                                         |

| 5              | 3BEN               | 0                | Clearing bit disables 3B.                                                                                                            |

| 6              | 3BUV               | 0                | Setting bit prevents enabling unless OUT3B < bleed down threshold.                                                                   |

| 7              | 3BDS               | 0                | Clearing bit disconnects OUT3B bleed down resistor.                                                                                  |

|                | d/Write system co  | _                |                                                                                                                                      |

| 0              | PPTEST             | 0                | 12-V pulldown test pin. Setting pin pulls the PASSx and BLKx pins to 0 V.                                                            |

| 1              | FLTMODE            | 0                | Clearing bit latchs off channels after over-current fault. Setting bit allows channels to automatically attempt restart after fault. |

| 2              | SPARE              | 0                | This bit must always be set to 0.                                                                                                    |

| 3              | 3ORON              | 0                | Setting bit enables 3A and 3B to prevent reverse current flow.                                                                       |

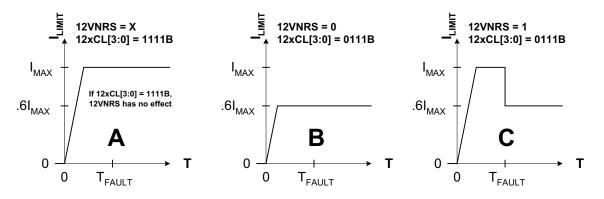

| 4              | 12VNRS             | 0                | Non Redundant System in rush control bit. Setting bit allows increased inrush current                                                |

| 4              |                    | 0                | in 12A and 12B with proper setting of 12xCLx bits.                                                                                   |

| 5              | AIRM               | 0                | Setting this masking bit prevents REG7 bits 3:0 from setting IRPT.                                                                   |

| 6              | BIRM               | 0                | Setting this masking bit prevents REG7 bits 7:4 from setting IRPT.                                                                   |

| 7              | DCC                | 0                | Setting bit allows the 12 V channels to operate despite loss of 3.3 V. This bit should be low for uTCA and AMC applications          |

| Register 7 Rea | d only latched IRP | T channel statu  | indicators, cleared on read                                                                                                          |

| 0              | 12APG              | 0                | Latches high when OUT12A goes from above $V_{TH\_PG}$ to below $V_{TH\_PG}.$                                                         |

| 1              | 12AFLT             | 0                | Latches high when 12A fault timer has run out.                                                                                       |

| 2              | 3APG               | 0                | Latches high when OUT3A goes from above $V_{TH\_PG}$ to below $V_{TH\_PG}.$                                                          |

| 3              | 3AFLT              | 0                | Latches high when 3A fault timer has run out.                                                                                        |

| 4              | 12BPG              | 0                | Latches high when OUT12B goes from above $V_{TH_PG}$ to below $V_{TH_PG}$ .                                                          |

| 5              | 12BFLT             | 0                | Latches high when 12B fault timer has run out.                                                                                       |

| 6              | 3BPG               | 0                | Latches high when OUT3B goes from above $V_{TH_PG}$ to below $V_{TH_PG}$ .                                                           |

| 7              | 3BFLT              | 0                | Latches high when 3B fault timer has run out.                                                                                        |

| Register 8 Rea | d only latched ove | ercurrent indica | tors, cleared on Read                                                                                                                |

| 0              | 12AOC              | 0                | Latches high when 12A enters over-current.                                                                                           |

| 1              | 12AFTR             | 0                | Latches high if 12A fast trip threshold exceeded.                                                                                    |

| 2              | 3AOC               | 0                | Latches high when 3A enters over-current.                                                                                            |

| 3              | 3AFTR              | 0                | Latches high if 3A fast trip threshold exceeded.                                                                                     |

| 4              | 12BOC              | 0                | Latches high when 12B enters over-current.                                                                                           |

| 5              | 12BFTR             | 0                | Latches high if 12B fast trip threshold exceeded.                                                                                    |

| 6              | 3BOC               | 0                | Latches high when 3B enters over-current.                                                                                            |

| 7              | 3BFTR              | 0                | Latches high if 3B fast trip threshold exceeded.                                                                                     |

|                | d only unlatched I |                  |                                                                                                                                      |

| 0              | 12ABS              | -                | High indicates BLKA commanded high.                                                                                                  |

| 1              | 12APS              | -                | Low indicates $V_{PASSA} > V_{OUT12A} + 61 V.$                                                                                       |

| 2              | 3ABS               | -                | Low indicates IN3A > OUT3A.                                                                                                          |

| 3              | 12BBS              | -                | High indicates BLKB commanded high.                                                                                                  |

| 4              | 12BPS              | -                | Low indicates $V_{PASSB} > V_{OUTB} + 61 V.$                                                                                         |

|                | 3BBS               | -                | Low indicates IN3B > OUT3B.                                                                                                          |

| 5              |                    |                  |                                                                                                                                      |

| 5              | 3AGS               | _                | Low indicates channel 3A gate is driven on ( $V_{GATE}$ > ( $V_{IN}$ + 1.75 V ).                                                     |

# **Detailed Description of Registers**

#### **Register 0**

| Table 5. Register 0. Channel 12A Configuration (Read/write) |        |         |                                                                 |  |  |  |

|-------------------------------------------------------------|--------|---------|-----------------------------------------------------------------|--|--|--|

| BIT                                                         | NAME   | DEFAULT | DESCRIPTION                                                     |  |  |  |

| 0                                                           | 12ACL0 | 1       | Clearing bit reduces 12A current limit & fast threshold by 5%.  |  |  |  |

| 1                                                           | 12ACL1 | 1       | Clearing bit reduces 12A current limit & fast threshold by 10%. |  |  |  |

| 2                                                           | 12ACL2 | 1       | Clearing bit reduces 12A current limit & fast threshold by 20%. |  |  |  |

| 3                                                           | 12ACL3 | 1       | Clearing bit reduces 12A current limit & fast threshold by 40%. |  |  |  |

| 4                                                           | 12APG0 | 1       | Clearing bit reduces 12A power good threshold by 600 mV.        |  |  |  |

| 5                                                           | 12APG1 | 1       | Clearing bit reduces 12A power good threshold by 1.2 V.         |  |  |  |

| 6                                                           | 12AHP  | 0       | Setting bit shifts 12A OR VTURNOFF from -3 mV to +3 mV nominal. |  |  |  |

| 7                                                           | 12AOR  | 1       | Clearing bit turns off 12A ORing FET by pulling BLKA low.       |  |  |  |

### Table 3. Register 0: Channel 12A Configuration (Read/write)

**12ACL[3:0]** These four bits adjusts the 12A current limit and fast trip threshold using the I<sup>2</sup>C interface. Setting the bits to 1111B places the 12A current limit at its maximum level, corresponding to 675 mV at SUM12A. The fast trip threshold then equals 100 mV. Clearing all bits reduces the current limit and fast trip threshold to 25% of these maximums.

**12APG[1:0]** These two bits adjust the 12A power good threshold. Setting the bits to 11B places the power good threshold at its maximum level of 10.5 V. Setting the bits to 00B places the threshold at its minimum level of 8.7 V. The lower thresholds may prove desirable in systems that routinely experience large voltage droops.

**12AHP** Setting this bit moves the 12A ORing turn off threshold from –3 mV to +3 mV. A positive threshold prevents reverse current from flowing through the channel, but it may cause the ORing FET to repeatedly cycle on-and-off if the load cannot maintain the required positive voltage drop across the combined resistance of the external FETs and the sense resistor. For further information, see Adjusting Oring Turn Off threshold For High Power Loads section

**12AOR** Clearing this bit forces the BLKA pin low, keeping the 12A ORing FET off. Clearing this bit does not prevent current from flowing through the FET's body diode.

www.ti.com

### **Register 1**

| BIT | NAME   | DEFAULT | DESCRIPTION                                                         |  |  |

|-----|--------|---------|---------------------------------------------------------------------|--|--|

| 0   | 12AFT0 | 1       | Setting bit increases 12A fault time by 0.5 ms.                     |  |  |

| 1   | 12AFT1 | 0       | Setting bit increases 12A fault time by 1 ms.                       |  |  |

| 2   | 12AFT2 | 0       | Setting bit increases 12A fault time by 2 ms.                       |  |  |

| 3   | 12AFT3 | 0       | Setting bit increases 12A fault time by 4 ms.                       |  |  |

| 4   | 12AFT4 | 0       | Setting bit increases 12A fault time by 8 ms.                       |  |  |

| 5   | 12AEN  | 0       | Clearing bit disables 12A by pulling PASSA and BLKA to 0 V.         |  |  |

| 6   | 12AUV  | 0       | Setting bit prevents enabling unless OUT12A < bleed down threshold. |  |  |

| 7   | 12ADS  | 0       | Clearing bit disconnects OUT12A bleed down resistor.                |  |  |

#### Table 4. Register 1: Channel 12A Configuration (Read/write)

**12AFT[4:0]** These five bits adjust the 12A channel fault time. The least-significant bit has a nominal weight of 0.5 ms, so fault times ranging from 0.5 ms (for code 00001B) to 15.5 ms (for code 11111B) can be programmed. In general the shortest fault time that fully charges downstream bulk capacitors without generating a fault should be used. Once the load capacitors have fully charged, the fault time can be reduced to provide faster short circuit protection. See Setting Fault Time section.

**12AEN** This bit serves as a master enable for channel 12A. Setting this bit allows the 12A channel to operate normally. Clearing this bit disables the channel by pulling PASSA and BLKA low.

**12AUV** Setting this bit prevents channel 12A from turning on until OUT12A falls below the bleed down threshold of 100 mV. This feature ensures that downstream devices reset by requiring their supply voltage to fall to nearly zero before the channel can enable them.

**12ADS** Clearing this bit disconnects the bleed down resistor that otherwise connects from OUT12A to ground. Systems using redundant power supplies should clear 12ADS to prevent the bleed down resistor from continuously sinking current.

www.ti.com

#### Register 2

|     |       | 0       | 5                                                                  |

|-----|-------|---------|--------------------------------------------------------------------|

| BIT | NAME  | DEFAULT | DESCRIPTION                                                        |

| 0   | 3AFT0 | 1       | Setting bit increases 3A fault time by 0.5 ms.                     |

| 1   | 3AFT1 | 0       | Setting bit increases 3A fault time by 1 ms.                       |

| 2   | 3AFT2 | 0       | Setting bit increases 3A fault time by 2 ms.                       |

| 3   | 3AFT3 | 0       | Setting bit increases 3A fault time by 4 ms.                       |

| 4   | 3AFT4 | 0       | Setting bit increases 3A fault time by 8 ms.                       |

| 5   | 3AEN  | 0       | Clearing bit disables 3A.                                          |

| 6   | 3AUV  | 0       | Setting bit prevents enabling unless OUT3A < bleed down threshold. |

| 7   | 3ADS  | 0       | Clearing bit disconnects OUT3A bleed down resistor.                |

#### Table 5. Register 2: Channel 3A Configuration (Read/write)

**3AFT[4:0]** These five bits adjust the 3A channel fault time. The least-significant bit has a nominal weight of 0.5 ms, so fault times ranging from 0.5 ms (for code 00001B) to 15.5 ms (for code 11111B) can be programmed. In general the shortest fault time that fully charges downstream bulk capacitors without generating a fault should be used. See Setting Fault Time section.

**3AEN** This bit serves as a master enable for channel 3A. Setting this bit allows the 3A channel to operate normally, provided the EN3A pin is also asserted. Clearing this bit disables the channel by removing gate drive to the internal pass FET, regardless of the state of the EN3A pin.

**3AUV** Setting this bit prevents channel 3A from turning on until OUT3A falls below the bleed down threshold of 100 mV. This feature ensures that downstream devices reset by requiring their supply voltage to fall to nearly zero before the channel can enable them.

**3ADS** Clearing this bit disconnects the bleed down resistor that otherwise connects from OUT3A to ground. Systems using redundant power supplies should clear 3ADS to prevent the bleed down resistor from continuously sinking current.

www.ti.com

### **Register 3**

| BIT | NAME   | DEFAULT | DESCRIPTION                                                     |  |  |  |

|-----|--------|---------|-----------------------------------------------------------------|--|--|--|

| 0   | 12BCL0 | 1       | Clearing bit reduces 12B current limit & fast threshold by 5%.  |  |  |  |

| 1   | 12BCL1 | 1       | Clearing bit reduces 12B current limit & fast threshold by 10%. |  |  |  |

| 2   | 12BCL2 | 1       | Clearing bit reduces 12B current limit & fast threshold by 20%. |  |  |  |

| 3   | 12BCL3 | 1       | Clearing bit reduces 12B current limit & fast threshold by 40%. |  |  |  |

| 4   | 12BPG0 | 1       | Clearing bit reduces 12B power good threshold by 600 mV.        |  |  |  |

| 5   | 12BPG1 | 1       | Clearing bit reduces 12B power good threshold by 1.2 V.         |  |  |  |

| 6   | 12BHP  | 0       | Setting bit shifts 12B OR VTURNOFF from -3 mV to +3 mV nominal. |  |  |  |

| 7   | 12BOR  | 1       | Clearing bit turns off 12B ORing FET by pulling BLKB low.       |  |  |  |

### Table 6. Register 3: Channel 12B Configuration (Read/write)

**12BCL[3:0]** These four bits adjusts the 12B current limit and fast trip threshold using the I<sup>2</sup>C interface. Setting the bits to 1111B places the 12B current limit at its maximum level, corresponding to 675 mV at SUM12B. The fast trip threshold then equals 100 mV. Clearing all bits reduces the current limit and fast trip threshold to 25% of these maximums.

**12BPG[1:0]** These two bits adjust the 12B power good threshold. Setting the bits to 11B places the power good threshold at its maximum level of 10.5 V. Setting the bits to 00B places the threshold at its minimum level of 8.7 V. The lower thresholds may prove desirable in systems that routinely experience large voltage droops.

**12BHP** Setting this bit moves the 12B ORing turn off threshold from –3 mV to +3 mV. A positive threshold prevents reverse current from flowing through the channel, but it may cause the ORing FET to repeatedly cycle on-and-off if the load cannot maintain the required positive voltage drop across the combined resistance of the external FETs and the sense resistor. For further information, see Adjusting ORing Turn Off threshold For High Power Loads section.

**12BOR** Clearing this bit forces the BLKB pin low, keeping the 12B ORing FET off. Clearing this bit does not prevent current from flowing through the FET's body diode.

www.ti.com

#### **Register 4**

| ріт | NAME   |         | DESCRIPTION                                                         |

|-----|--------|---------|---------------------------------------------------------------------|

| BIT |        | DEFAULT | DESCRIPTION                                                         |

| 0   | 12BFT0 | 1       | Setting bit increases 12B fault time by 0.5 ms.                     |

| 1   | 12BFT1 | 0       | Setting bit increases 12B fault time by 1 ms.                       |

| 2   | 12BFT2 | 0       | Setting bit increases 12B fault time by 2 ms.                       |

| 3   | 12BFT3 | 0       | Setting bit increases 12B fault time by 4 ms.                       |

| 4   | 12BFT4 | 0       | Setting bit increases 12B fault time by 8 ms.                       |

| 5   | 12BEN  | 0       | Clearing bit disables 12B by pulling PASSB and BLKB to 0 V.         |

| 6   | 12BUV  | 0       | Setting bit prevents enabling unless OUT12B < bleed down threshold. |

| 7   | 12BDS  | 0       | Clearing bit disconnects OUT12B bleed down resistor.                |

#### Table 7. Register 4: Channel 12B Configuration (Read/write)

**12BFT[4:0]** These five bits adjust the 12B channel fault time. The least-significant bit has a nominal weight of 0.5 ms, so fault times ranging from 0.5 ms (for code 00001B) to 15.5 ms (for code 11111B) can be programmed. In general the shortest fault time that fully charges downstream bulk capacitors without generating a fault should be used. Once the load capacitors have fully charged, the fault time can be reduced to provide faster short circuit protection. See Setting Fault Time section.

**12BEN** This bit serves as a master enable for channel 12B. Setting this bit allows the 12B channel to operate normally. Clearing this bit disables the channel by pulling PASSB and BLKB low.

**12BUV** Setting this bit prevents channel 12B from turning on until OUT12B falls below the bleed down threshold of 100 mV. This feature ensures that downstream devices reset by requiring their supply voltage to fall to nearly zero before the channel can enable them.

**12BDS** Clearing this bit disconnects the bleed down resistor that otherwise connects from OUT12B to ground. Systems using redundant power supplies should clear 12BDS to prevent the bleed down resistor from continuously sinking current.

www.ti.com

### **Register 5**

| BIT | NAME  | DEFAULT | DESCRIPTION                                                        |

|-----|-------|---------|--------------------------------------------------------------------|

| 0   | 3BFT0 | 1       | Setting bit increases 3B fault time by 0.5 ms.                     |

| 1   | 3BFT1 | 0       | Setting bit increases 3B fault time by 1 ms.                       |

| 2   | 3BFT2 | 0       | Setting bit increases 3B fault time by 2 ms.                       |

| 3   | 3BFT3 | 0       | Setting bit increases 3B fault time by 4 ms.                       |

| 4   | 3BFT4 | 0       | Setting bit increases 3B fault time by 8 ms.                       |

| 5   | 3BEN  | 0       | Clearing bit disables 3B.                                          |

| 6   | 3BUV  | 0       | Setting bit prevents enabling unless OUT3B < bleed down threshold. |

| 7   | 3BDS  | 0       | Clearing bit disconnects OUT3B bleed down resistor.                |

#### Table 8. Register 5: Channel 3B Configuration (Read/write)

**3BFT[4:0]** These five bits adjust the 3B channel fault time. The least-significant bit has a nominal weight of 0.5 ms, so fault times ranging from 0.5 ms (for code 00001B) to 15.5 ms (for code 11111B) can be programmed. In general the shortest fault time that fully charges downstream bulk capacitors without generating a fault should be used. See Setting Fault Time section.

**3BEN** This bit serves as a master enable for channel 3B. Setting this bit allows the 3B channel to operate normally, provided the EN3B pin is also asserted. Clearing this bit disables the channel by removing gate drive to the internal pass FET, regardless of the state of the EN3B pin.

**3BUV** Setting this bit prevents channel 3B from turning on until OUT3B falls below the bleed down threshold of 100 mV. This feature ensures that downstream devices reset by requiring their supply voltage to fall to nearly zero before the channel can enable them.

**3BDS** Clearing this bit disconnects the bleed down resistor that otherwise connects from OUT3B to ground. Systems using redundant power supplies should clear 3BDS to prevent the bleed down resistor from continuously sinking current.

#### **Register 6**

| BIT | NAME    | DEFAULT | DESCRIPTION                                                                                                                                   |

|-----|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PPTEST  | 0       | 12-V pulldown test pin. Asserting this pulls the PASSx and BLKx pins to 0 V.                                                                  |

| 1   | FLTMODE | 0       | Clearing bit forces channels to latch off after over-current fault. Setting bit allows channels to automatically attempt restart after fault. |

| 2   | SPARE   | 0       | This bit must always be set to 0.                                                                                                             |

| 3   | 30RON   | 0       | Setting bit enables 3A and 3B to prevent reverse current flow.Clearing bit disables 3A and 3B ORing.                                          |

| 4   | 12VNRS  | 0       | Non Redundant System in rush control bit. Setting bit allows increased inrush current in 12A and 12B.                                         |

| 5   | AIRM    | 0       | Setting this masking bit prevents REG7 bits 3:0 from setting IRPT.                                                                            |

| 6   | BIRM    | 0       | Setting this masking bit prevents REG7 bits 7:4 from setting IRPT.                                                                            |

| 7   | DCC     | 0       | Setting bit allows the 12 V channels to operate despite loss of 3.3 V. For uTCA and AMC applications this bit should be low.                  |

Table 9. Register 6: System Configuration (Read/write)

**PPTEST** This bit is used for testing the fast turnoff feature of the PASSx and BLKx pins. Setting this bit enables the fast turnoff drivers for all four pins. Clearing this bit restores normal operation. PPTEST allows the fast turnoff drivers to operate at full current indefinitely, whereas they would normally operate for only about 15 S. While using PPTEST the energy dissipated in the fast turnoff drivers must be externally limited to 1 mJ per driver to prevent damage to the TPS2359.

**FLTMODE** Setting this bit allows a channel to attempt an automatic restart after an overcurrent condition has caused it to time out and shut off. The retry interval equals approximately 100 times the programmed fault time. The FLTMODE bit affects all four channels. If cross-connection is enabled (DCC = 0), a fault on channel 3A turns off channel 12A, and a fault on channel 3B turns off channel 12B. If a 3.3-V channel automatically restarts because FLTMODE = 1, the associated 12-V channel remains disabled until its enable bit (12AEN or 12BEN) is cycled on and off.

**SPARE** This bit must always be set to 0.

**30RON** Setting this bit allows the 3.3-V ORing function to operate normally. Clearing this bit prevents the 3.3-V channels from disabling if their output voltage exceeds their input voltage . This bit is typically cleared for non-redundant systems.

**12VNRS** Setting this bit increases the current limit for either 12-V channel to its maximum value during the initial inrush period that immediately follows the enabling of the channel. During inrush, the current limit behaves as if 12xCL[3:0] = 1111B. After the current drops below this limit, signifying the end of the inrush period, the current limit returns to normal operation.

AIRM Setting this bit prevents the 12APG, 12AFLT, 3APG, and 3AFLT bits from setting the IRPT pin.

BIRM Setting this bit prevents the 12APG, 12BFLT, 3BPG, and 3BFLT bits from setting the IRPT pin.

**DCC** Setting this bit disables cross-connection. If DCC = 0, when a 3.3-V channel experiences a fault, both it and its associated 12-V channel turn off. Specifically, a fault on channel 3A turns off channel 12A, and a fault on channel 3B turns off channel 12B. If DCC = 1, then the 12-V channels continue to operate even if their associated 3.3-V channels experience faults.

www.ti.com

### Register 7

### Table 10. Register 7: Latched IRPT Channel Status Indicators (Read-only, cleared on read)

| BIT | NAME   | DEFAULT | DESCRIPTION                                                                  |

|-----|--------|---------|------------------------------------------------------------------------------|

| 0   | 12APG  | 0       | Latches high when OUT12A goes from above $V_{TH_PG}$ to below $V_{TH_PG}$ .  |

| 1   | 12AFLT | 0       | Latches high when 12A fault timer has run out.                               |

| 2   | 3APG   | 0       | Latches high when OUT3A goes from above $V_{TH\_PG}$ to below $V_{TH\_PG}.$  |

| 3   | 3AFLT  | 0       | Latches high when 3A fault timer has run out.                                |

| 4   | 12BPG  | 0       | Latches high when OUT12B goes from above $V_{TH\_PG}$ to below $V_{TH\_PG}.$ |

| 5   | 12BFLT | 0       | Latches high when 12B fault timer has run out.                               |

| 6   | 3BPG   | 0       | Latches high when OUT3B goes from above $V_{TH_PG}$ to below $V_{TH_PG}$ .   |

| 7   | 3BFLT  | 0       | Latches high when 3B fault timer has run out.                                |

**12APG** This bit is set if the voltage on OUT12A drops below the power-good threshold set by the 12APG[1:0] bits, and it remains set until Register 7 is read. If AIRM = 0, setting this bit asserts the IRPT pin.

**12AFLT** This bit is set if the fault timer on channel 12A has run out, and it remains set until Register 7 is read. If AIRM = 0, setting this bit asserts the IRPT pin.

**3APG** This bit is set if the voltage on OUT3A drops below the power-good threshold, and it remains set until Register 7 is read. If AIRM = 0, setting this bit asserts the IRPT pin.

**3AFLT** This bit is set if the fault timer on channel 3A has run out, and it remains set until Register 7 is read. If AIRM = 0, setting this bit asserts the  $\overline{IRPT}$  pin.

**12BPG** This bit is set if the voltage on OUT12B drops below the power-good threshold set by the 12BPG[1:0] bits, and it remains set until Register 7 is read. If BIRM = 0, setting this bit asserts the IRPT pin.

**12BFLT** This bit is set if the fault timer on channel 12B has run out, and it remains set until Register 7 is read. If BIRM = 0, setting this bit asserts the IRPT pin.

**3BPG** This bit is set if the voltage on OUT3B drops below the power-good threshold, and it remains set until Register 7 is read. if BIRM = 0, setting this bit asserts the IRPT pin.

**3BFLT** This bit is set if the fault timer on channel 3B has run out, and it remains set until Register 7 is read. If BIRM = 0, setting this bit asserts the IRPT pin.

# www.ti.com Register 8

| Table 11. Register 8: Latched Status Indicators (Read-only, cleared on read) |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| BIT | NAME   | DEFAULT | DESCRIPTION                                       |

|-----|--------|---------|---------------------------------------------------|

| 0   | 12AOC  | 0       | Latches high when 12A enters over-current.        |

| 1   | 12AFTR | 0       | Latches high if 12A fast trip threshold exceeded. |

| 2   | 3AOC   | 0       | Latches high when 3A enters over-current.         |

| 3   | 3AFTR  | 0       | Latches high if 3A fast trip threshold exceeded.  |

| 4   | 12BOC  | 0       | Latches high when 12B enters over-current.        |

| 5   | 12BFTR | 0       | Latches high if 12B fast trip threshold exceeded. |

| 6   | 3BOC   | 0       | Latches high when 3B enters over-current.         |

| 7   | 3BFTR  | 0       | Latches high if 3B fast trip threshold exceeded.  |