基于HS3282的ARINC429航空通讯总线设计

摘要: 本文简要地介绍了航空电子通讯总线ARINC429接口的硬件设计和软件算法。系统设计中具有典型性和实用性。

关键词:航空电子;差分输出;航空429总线;环形队列

功能相对独立的航空电子系统逐步走向综合,例如将雷达、惯导、GPS和机载计算机联合,组成新型航空图导航系统,各子系统之间的数据通讯变得尤为重要。航空电子系统之间最常的通讯总线是ARINC429和1553B。其中ARINC429广泛使用在波音(Boeing)系列飞机、欧洲空中客车(Airbus)等机种。我国的惯导系统也以ARINC429为主要通讯总线。

一. ARINC429总线简介

ARINC429规范,又称Mark33数字信息传输系统(DITS---Digital Information Transfer System),是专为航空电子系统通讯而规定的航空工业标准,解决了原来419规范的许多矛盾和冲突。它忽略了不同厂家航电系统接口的复杂性,为系统互联提供了统一平台。根据规范,数字信息通过一对单向、差分耦合、双绞屏蔽线传输,本质属于串行通讯范畴。数据以32-Bit字(Word)格式传送。每个字包含1-Bit校验位,8-Bit标号。标号(Label)定义了飞行数据的功能,即保持被传输数据的所属类型,例如属于精度数据、纬度数据等。其余的数据位或以数字(二进制或BCD编码),或以字母编码,根据Label而区分成不同的域。为了使通讯完全标准化和防止冲突,所有的飞行功能都已经赋予了特定的标号和数据格式。

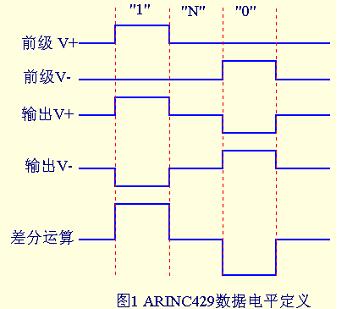

ARINC429数据发送时经过二级差分驱动,如图1波形所示。前级V+、V-是TTL电平,即逻辑1为5V,逻辑0为0V的正逻辑。经过驱动的第二级输出V+、V-电平和参考电压VRef有关。而差分运算结果是参考电压的2倍。图1表示ARINC429逻辑“1”、“Null”空数据和逻辑“0”在差分双绞线上电平定义。在连续传送数据时,每个32-Bit字之间至少插入4个空(Null)状态进行隔离,亦即字间隙。字内格式定义如表1所示。注意,其位号从1开始,不是通常的从0开始的习惯。

表1 ARINC429 32-Bit字格式定义

|

ARINC BIT# (数据位) |

Function (功能) |

备注 |

|

1---8 |

Label |

标号 域 |

|

9---10 |

SDI or Data |

数据源(Source)、目的(Destination) 或 数据的一部分 |

|

11 |

LSB |

|

|

12-27 |

Data |

|

|

28 |

MSB |

|

|

29 |

Sign |

数据的最低有效位 |

|

30,31 |

SSM |

数据 |

|

32 |

Parity Status |

数据的最高有效位 |

二. HS3282芯片和ARINC429收发设计

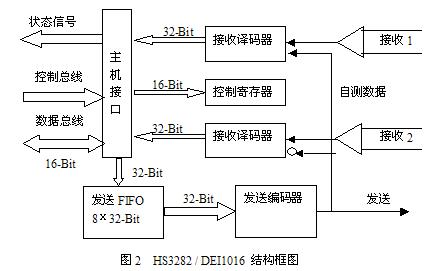

目前ARINC429收发器以HARRIS公司的HS3282和HS3182最为著名,分别和Device Engineering公司的DEI1016及BD429完全兼容。HS3282是高性能的CMOS型429接口,亦能满足类似的时分多路串行数据通讯。图2是其结构框图, 整个芯片只需单5V工作电源。它具有2路接收、一路发送。接收器和发送器相互独立,同时工作。双通道接收器之间也是独立的并行接收,可以直接连接到ARINC429总线,而不需电平转换。数据字长可以是标准的32-Bit或25-Bit,接收数据时进行校验,而发送数据时产生校验。内部定时器可自动调整字间隙(Word Gap)。其发送缓冲是一个8ⅹ32Bit的FIFO。

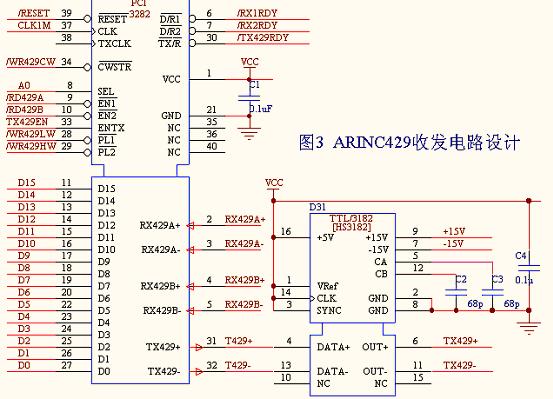

HS3282和CPU接口比较简单,发送时经常和HS3182配合。HS3182是满足ARINC429规范的、双极数据输入的线驱动器。这里不再详细介绍这两个芯片的管脚分配,如需要可以参考图3。

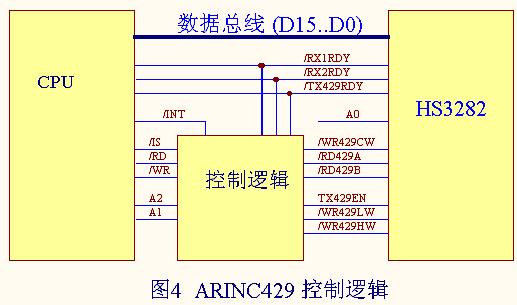

图3是ARINC429总线收发的经典电路。复位是低电平有效,外部工作时钟为1MHz。具有二路接收,即第一路接收(Rx429A+,Rx429A-)和第二路接收(Rx429B+,Rx429B-),具有一路发送,即(Tx429+,Tx429-)。发送时,HS3282为前级输出,HS3182为正式差分输出。C2、C3为68pF的电容,这两个电容至关重要,最好采用高精度军品电容。一般作为CPU外围I/O设备的接口芯片,都有片选、读、写信号和选择片内寄存器的若干地址线。但HS3282有点特殊,每一个寄存器操作信号都需要对CPU信号进行译码产生。图4是对HS3282控制逻辑示意图。选择CPU时最好直接选择外部数据总线为16-Bit以上的,如MC80186、F240等。如果非要用8-Bit的CPU,则需要2个8-Bit的锁存器,一次将16-Bit先读写到锁存器中,然后分别对2个锁存器读写,硬件和软件都比较麻烦。控制逻辑以CPU提供的I/O操作信号/IS和读写信号/RD、/WR以及地址A2A1为输入,为HS3282产生操作信号,诸如读第一路接收数据寄存器信号 /RD429A,第二路 /RD429B,发送低字选通信号 /WR429LW,高字 /WR429HW,发送使能控制 TX429EN等。控制逻辑和CPU同时监视HS3282的3个状态信号,第一路接收准备好信号 /Rx1RDY,第二路/Rx2RDY,发送准备好/Tx429RDY。这些状态信号一方面可供软件查询,另一方面由控制逻辑产生 /INT中断请求。

在图4和下面的逻辑描述中都没有体现为CPU提供READY信号的要求。一般情况下,作为I/O外设的HS3282读写速度要比CPU慢,应该用一个状态机进行速度匹配,为CPU产生READY信号。表2是对图4控制逻辑电路地址的一种分配方法,并不是唯一的。在发送使能信号TX429EN控制中,简单地把发送准备好信号 /TX429RDY反相后输出。亦即只要HS3282发送器有空闲,就允许发送。HS3282的发送器包括一个FIFO,可以存储8个32-Bit的429数据字。在要求爆发式(Burst)发送时,可以把发送使能TX429EN直接由CPU控制。一般处于禁止状态,当CPU填充HS3282的发送FIFO字数达到自定数目(如8个)时,再使能发送,使FIFO中数据倾泻而出。

表2 HS3282寄存器分配

|

地址 |

读操作 (Read) |

写操作(Write) |

有效信号 |

|

00H |

第一路接收低字寄存器 Rx429ALW |

|

/RD429A = L, (SEL=A0=0) |

|

01H |

第一路接收高字寄存器 Rx429AHW |

|

/RD429A = L, (SEL=A0=1) |

|

02H |

第二路接收低字寄存器 Rx429BLW |

|

/RD429A = L, SEL=A0=0 |

|

03H |

第二路接收高字寄存器 Rx429BHW |

控制寄存器 CR429A |

/RD429B =L, (SEL=A0=1) |

|

04H |

|

发送低字寄存器 Tx429ALW |

/WR429LW = L |

|

05H |

|

|

|

|

06H |

|

发送高字寄存器 Tx429AHW |

/WR429HW = L |

其实现逻辑如下:

IS,RD,WR pin; // CPU方的I/O操作、读写信号,皆为低有效.

IOAddr = [A2,A1,X]; // CPU 方 I/O 地址

… …

ENTX429A = !TX429ARDY; // ARINC429 发送使能.

// 读 第一路 ARCIN429 接收寄存器 高低字.

!RD429A = !IS & !RD &

((IOAddr == RX429ALW) # (IOAddr == RX429AHW));

// 读 第二路 ARCIN429 接收寄存器 高低字.

!RD429B = !IS & !RD &

((IOAddr == RX429BLW) # (IOAddr == RX429BHW));

// 写 第一路 ARCIN429 发送寄存器 高低字.

!WR429AL = !IS & !WR & (IOAddr == TX429ALW);

!WR429AH = !IS & !WR & (IOAddr == TX429AHW);

// 写 第一片 HS3282 控制寄存器.

!WR429ACW = !IS & !WR & (IOAddr == CR429A);

!INT = !RX1RDY # !RX2RDY; // 2路接收准备好,共享中断请求.

… …

三. 软件设计

上电复位后,软件应在正式工作前初始化HS3282,即向控制器写控制字。初始化时可以设置字长为32-Bit或25-Bit。外部提供的工作时钟为1MHz,内部接收和发送速率可以设置为十分之一或八十分之一,即100Kbps或12.5Kbps。也可以设置为自测试模式,即HS3282的发送直接在内部环接到第一路接收,反相接到第二路。发送数据,然后比较发送和接收,判断HS3282工作状况。自测试原理可以参考图1的框图。在此主要介绍正式工作时软件的一些功能算法。

3.1 原始数据收发

在图3和图4的硬件设计中已经考虑到软件设计的方便性。软件收发既可以采用查询HS3282的状态位进行,也可以采用中断驱动。原始数据的收发是整个系统的瓶颈,一般实用程序都采用中断接收,查询式发送。其中断响应作为核心部分,一般都使用对应嵌入式CPU的汇编语言实现。为清楚起见,采用算法语言描述。中断接收数据首先存放到缓冲区,亦即环形队列中,再由主程序读取,其结构与算法如下:

|

位置 |

0 |

1 |

2 |

3 … N-2 |

N-1 |

|

内容 |

RxNum |

WrPtr |

RdPtr |

Data Buffer |

EndAddr |

|

功能 |

当前接收字数 |

写指针 |

读指针 |

数据缓冲区 |

结束地址 |

// 环形队列缓冲区初始化

procedure InitBuf;

begin

Disable Interrupt; // 禁止中断

RxNum := 0; // 接收数目清0

WrPtr := StartAddr; // 写指针指向开始地址

RdPtr := StartAddr; // 读指针指向开始地址

Enable Interrupt; // 使能中断

end;

// ARINC429环形队列中断接收算法.

procedure Rx429Interrupt

begin

Save Register; // 保护现场

DataBuf[WrPtr] := InpW(Rx429ALW); // 读HS3282低16-Bit字

Increament(WrPtr); // 写指针加1,后移.

DataBuf[WrPtr] := InpW(Rx429AHW); // 读HS3282高16-Bit字

Increament(WrPtr); // 写指针加1,后移.

Disable Interrupt; // 禁止更高级中断.

Increament(RxNum); // 修改接收字数,即加1.

Enable Interrupt; // 开放中断

if (WrPtr ≥ EndAddr) then // 若写指针到达队尾,环绕之

WrPtr := StartAddr;

Restore Register; // 恢复现场

end;

// 环形队列读取算法.

function Rd429Buf(var LW429,HW429:word):boolean;

begin

Result := False;

if (Rx Num = 0) then exit; // 如果没有接收数据,则退出

Result := True; // 所读数据有效

LW 429 := DataBuf[RdPtr]; // 读队列429低16-Bit字

Increament(RdPtr); // 读指针加1,后移.

HW429 := DataBuf[RdPtr]; // 读队列429高16-Bit字

Increament(RdPtr); // 读指针加1,后移.

Disable Interrupt; // 禁止中断.

Decreament(RxNum); // 修改接收字数,即减1.

Enable Interrupt; // 开放中断

if (RdPtr ≥ EndAddr) then // 若读指针到达队尾,环绕之

RdPtr := StartAddr;

end;

环形队列初始化应该在系统开放中断前调用,接收算法本身就是中断响应,而读取算法在主程序中数据处理时调用。环形队列缓冲区大小应该和主程序处理速度取得平衡,太大则浪费空间,太小则容易溢出,造成混乱。

3.2 多路接收中断共享算法

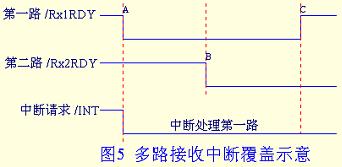

当2路以上接收共享一个中断时,容易出现覆盖现象,丢掉某一路数据,或使边沿触发的中断失效,不再接收任何数据。这种错误非常隐蔽,如图5波形。当在A点第一路准备号/Rx1RDY = L,/XINT有效,引起中断,CPU进入中断处理响应,在AB之间已经判定为第一路有效并开始处理。处理到B点时,第二路接收准备好亦引起中断。但/XINT已经有效,不会引起电平变化。中断响应程序继续进行,在C点退出,没有处理第二路接收。如果中断请求是电平 (Level) 敏感,中断处理退出后还可以再次进入。但有相当的系统开销。若中断请求是边沿(edge)触发,在C点退出之后,因未处理第二路接收使得中断请求 /INT一直保持电平有效,但不能产生边沿跳变翻转,中断触发条件永远不能满足,系统死锁。各路数据将无一幸免的丢失。

有人解决这个问题时采用“独占中断”办法,将每一路接收准备好只对应到一条硬件中断请求上。嵌入式CPU能提供给外部的硬件中断都比较少,系统外围设备较少时尚能对付,I/O外设和接收通道变多时就束手无策。实质性解决办法需要“软硬兼施”。如前图4所示,将HS3282的 /Rx1RDY,/Rx2RDY等状态信号同时送达CPU,组成只读“状态寄存器”,供CPU中断响应时查询。对中断处理方法如下:

// 多路共享中断处理程序算法

procedure RxShareIRQ

begin

Save Register; // 保护现场

while Data(/INT = L) do // 中断请求信号电平有效

begin

Read SR; // 读状态寄存器

Treat Receive // 根据状态,处理对应接收通道。

end;

Restore Register; // 恢复现场

end;

这个方法已经运用在多个不同种类的系统,证明是非常有效的。有人质疑在中断响应中使用循环是否合适,甚至认为在速度快、路数多的情况下CPU可能全消耗在中断循环中,仍然要丢数据。“哎呀,怎么得了”,岂不呜乎哀哉。其实,路数越多,这种办法越有效。它进入中断次数少,系统开销就少,对多路爆发式数据接收响应快。至于丢数据则更不可能,CPU一般都比外设处理速度快得多。如果CPU速度不足以管理几路接收,并进行一定的加工处理,还要这种“头重脚轻根底浅”的系统干什么?

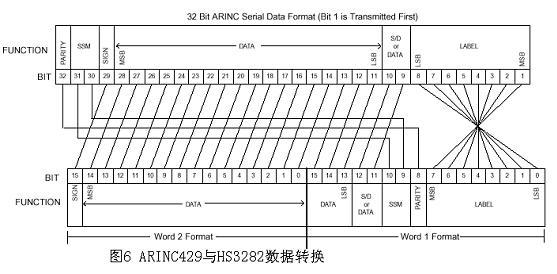

3.3 ARINC429字与HS3282数据转换

ARINC429的32-Bit逻辑字和HS3282数据线上2个16-Bit的物理字并不完全等同,在数据接收后的处理和发送前需要软件进行适当的转换。目前我国在SZ-01规范中规定数字信息传输系统采用HB6096标准,和上面规定差不多,只是把SDI、LSB、MSB统一规定到数据域,定义如下:

表3 HB6096标准

|

D32 |

D31-D30 |

D29 |

D28-D9 |

D8—D1 |

|

奇偶位 |

状态位 |

符号位 |

20位数据 |

8位标号 |

在和上层软件交换数据时,应以ARINC429字格式进行,而在控制HS3282收发时应以2个16-Bit物理字为单位。底层软件要进行互逆转换。总的转换方法如图6所示。注意,两者的标号逐位逆序对应,即D7 →D0等。以下是标号转换算法。

//-----------------------------------------------------

// function TransLabel(value:byte):byte;

// 功能: ARINC429数据标号互换

// 入口参数:

// value: 原标号值

// Result = 逐位转换后的新标号

//---------------------------------------------------

function TransLabel(value:byte):byte;

begin

Result := 0;

if ((value and $01) then Result := Result or $80; // 交换D0 ←→D7

if ((value and $02) then Result := Result or $40; // 交换D1 ←→D6

if ((Label and $04) then Result := Result or $20; // 交换D2 ←→D5

if ((value and $08) then Result := Result or $10; // 交换D3 ←→D4

if ((value and $10) then Result := Result or $08; // 交换D4 ←→D3

if ((value and $20) then Result := Result or $04; // 交换D5 ←→D2

if ((value and $40) then Result := Result or $02; // 交换D6 ←→D1

if ((value and $80) then Result := Result or $01; // 交换D7 ←→D0

end;

至于32-Bit的ARINC429数据和2个16-Bit的HS3282物理字的相互转换,可以参考上面标号互换方法,不再给出。

四. 结束语

HS-3282是为ARINC429度身定做的,而且设计针对现今飞机技术最苛刻的要求,所以使用HS-3282来设计ARINC429总线既简单、有效,又严格保证其可靠性。我们已将上述设计应用在多个不同种类的航空电子系统中,证明是十分有效的。随着航空电子系统之间的通讯标准向ARINC429总线靠拢,HS3282的应用将更加广泛。