基于TMS320C32和AMCCS5933的高速数据采集系统

摘 要:本文介绍了一种利用DSP和AMCCS5933实现高速数据的实时采集、存储和处理的方法,并根据自己

的实践经验对于设计和调试过程中可能出现的问题进行了阐述和分析。

关键词:DSP;AMCCS5933;高速数据采集

数据信号处理器能够高速地处理数据并具有强大的数字吞吐能力,在数据采集领域获得了广泛的应用。而PCI总线也因为极高的数据传输速率、与处理器无关、能支持多个外设等独特性能,逐渐成为数据采集领域微机总线的主流。本文中的采集系统就是利用TI的TMS320C32芯片和AMCC公司的AMCCS5933来搭建的。

系统结构与功能:

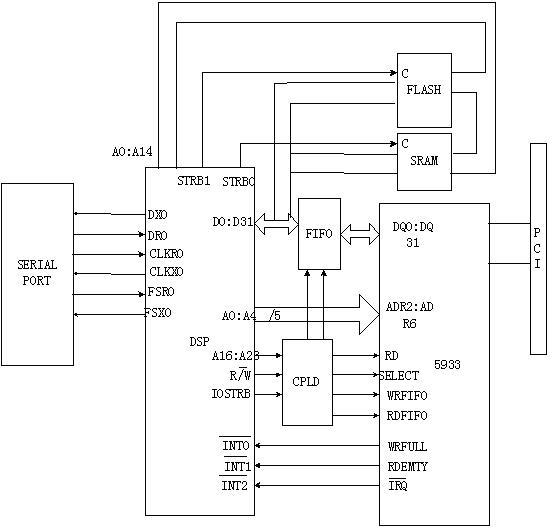

图1 数据采集系统框图

如图所示,该数据采集系统主要有DSP芯片、PCI接口芯片、CPLD芯片、缓存芯片FIFO构成。DSP芯片是一款32位的浮点芯片TMS320C32,它的主要功能是进行数据的采集,包括从串口进来的同步串行数据和从PCI总线传来的32位并行数据;另外它还可以对采集到的数据进行简单的处理,包括打包、分路等。

AMCCS5933是32位、33MHz的通用PCI总线控制器专用芯片,它符合PCI总线规范2.2版本。AMCCS5933既可以作PCI从设备,又可以作PCI主控设备。AMCCS5933为设计者提供了三种数据传输方式:PASS THRU 方式、FIFO 方式和 MAILBOX 方式。通过驱动程序对总线控制寄存器设置来控制总线操作和数据传输。总线控制寄存器有两组:PCI总线控制寄存器和本地总线控制寄存器,分别用来控制PCI总线和本地总线操作。

CPLD芯片是DSP和PCI之间能够正常进行数据传输的枢纽,其主要功能是控制二者之间的读写时序,以保证不丢失数据和不采集到错误的数据。由于在PCI总线控制器S5933的FIFO中只有8 个32 位寄存器,实时传送高速数据时,AMCCS5933内部的FIFO很快就会满,而外界的数据仍会源源不断地传送过来,可能会造成数据的丢失。因此,必须对数据的缓存进行扩展。在本系统中采用一片双口FIFO实现这项功能。

基本工作原理:

接收数据时TMS320C32串行口将接收到的同步串行信号转换成32位的并行信号,并传送到32位FIFO的输入端,当FIFO的半满信号有效时,CPLD逻辑控制芯片检查PCI总线控制器AMCCS5933是否准备好,如果准备好,则CPLD控制逻辑向FIFO发出准备好信号,同时使FIFO 的读写使能信号REN 和WEN有效。数据写入S5933内部缓存的过程中如果出现WRFULL变高,即内部FIFO满时,则向TMS320C32发出中断请求,C32监测到中断信号转入等待状态,直到应用程序将数据读走。

发送数据时,S5933读取PCI总线传送来的32位数据到内部FIFO中,C32判断AMCCS5933内部FIFO的状态,如果为空则等待,否则向CPLD发出准备好信号,同时使FIFO的读些使能信号REN和WEN有效,在外部时钟的控制下将数据读入到SRAM中并从串口发送出去。

系统硬件设计:

整个硬件系统主要由DSP芯片和PCI接口控制芯片及数据链路控制芯片组成。

1.DSP数据采集芯片TMS320C32

DSP芯片采用TI公司的TMS320C32-60,它是一款32位的浮点芯片,指令周期为33ns,330MOPS,24位地址,两个DMA通道,改进型外部存储器接口支持8/16/32位数据的访问。它支持多种boot loader 方式,并可以重新定位中断向量表。在本系统中,它主要是起到数据转发的功能,同时在传输时间允许的情况下还能够对数据做简单的处理。

2.PCI总线接口芯片AMCCS5933

AMCCS5933在本系统中起一个桥路的作用,即它是PCI总线和本地总线之间的桥路。它是通过外挂的EEPROM来设置配置空间的,可以通过AMCC的七个NVBULDER软件对EEPROM进行读写。AMCCS5933内部有8个MAILBOX:4个输出MAIXBOX和4个输入MAIXBOX 。主要用于主机方与本地逻辑之间的通信,例如传输一些自定义的控制字、状态信息等。主机对MAIXBOX的访问通过I/O读写来完成,本地逻辑对MAILBOX的访问则通过本地控制寄存器的方式来完成。

3.CPLD芯片

当数据从DSP传到PCI 总线时,CPLD芯片读取AMCCS5933内部FIFO的空满状态,若为满状态WRFULL有效则等待,直到主机把数据读走再使WRFIFO有效,向FIFO中写入数据;当数据从PCI传到DSP时,CPLD若判断读空状态RDEMPTY有效则使RDFIFO无效,直到FIFO为非空状态。

4.本系统中数据主要是利用AMCCS5933的FIFO方式进行传输的,因此这里着重介绍一下FIFO方式下的数据传输。

4.1基本数据传输

AMCCS5933内部有两个单向FIFO:输出FIFO和输入FIFO,主机和本地逻辑可以以访问控制寄存器的方式来访问FIFO,也可以通过WRFIFO#、RDFIFO#、WRFULL、RDEMPTY、BPCLK这几个引脚来直接读写FIFO。在设计当中一般采用后一种方法。直接读写FIFO有两种工作方式:同步方式和异步方式。在同步方式下,WRFIFO#、RDFIFO#为FIFO读些使能信号,在BPCLK的上升沿写入和读出数据,输出引脚BPCLK输出33MHz信号。在异步方式下,WRFIFO#、RDFIFO#为FIFO读写信号。WRFIFO为输出FIFO满信号,RDFIFO为输入FIFO空信号。

4.2 DMA的实现

在FIFO方式下可以实现DMA传输。

DMA传输的实现步骤:

(1) 通过NVBULDER软件设置DMA传输的控制方为主机或本地逻辑;

(2) 设置有关的PCI总线控制寄存器。

MWAR DMA 写地址寄存器,填入接收数据存放的起始地址

MWTC DMA 写计数器,填入接收数据的字节数

MRAR DMA 读抵制寄存器,填入发送数据起始地址

MRTC DMA 读计数器,填入发送数据的字节数

(3) 启动DMA传输

通过设置MCSR寄存器启动DMA传输。

由本地逻辑控制的DMA传输步骤,只需将控制方式改为本地逻辑控制,然后由本地逻辑来设置相应的寄存器。

5.硬件设计中应注意的问题

为保证调试工作的顺利进行,硬件设计中应注意以下几个方面的问题:

(1) 认真处理好复位和时钟信号,包括不同元器件之间复位的先后时序及看门狗的喂给信号;

(2) 要采用四层以上的线路板,每个电源点和地之间必须经过0.1uF的退耦电容,最后单点连接电源和地;

(3) 晶振频率高于60MHz时,最难以解决的问题是高频干扰问题,因此在布线时应尽量使高频线短而粗,且远离易受干扰的信号线;

(4) 布线时必须考虑两线之间的线间距及相邻两条平行线的长度,采用减少高频线的长度或在两条并行线之间插入一条地线;

(5) 充分考虑信号的完整性问题,包括反射、振铃、地弹、串扰等。

驱动程序和数据采集软件设计:

PCI数据采集卡的一个关键问题是驱动程序的开发。设备驱动程序提供链接到PCI板卡的软件接口,文件扩展名为.SYS的动态链接库。在Windows98 和 Windows2000中,设备驱动程序必须根据Windows驱动程序模型(WDM)设计。设备驱动程序的关键是如何完成硬件操作,基本功能使完成设备的初始化、对端口的读写操作、中断的设备和响应及中断的调用,以及对内存的直接读写。

设计数据采集软件的时候要考虑到高速数据的实时、稳定传输,要综合考虑主机主板及硬盘的性能。应尽量减少数据接收时使用的线程,使CPU可以全速用于数据的接收。

硬件调试:

设计并加工好印刷电路板后就可以进入硬件调试阶段。在这个阶段,首先应对电路板进行细致的常规检查,防止短路和断路现象。加电后,应检查各芯片的电源引脚电压是否正常,晶振是否振荡,复位是否正确可靠。在做完这些基本检查之后就可以进行系统硬件调试了。

调试过程中建议采用从小到大、由易到难的方式,即先焊接一部分芯片,加电测量其电压电流特性,若有问题,则在这部分小的范围内将其解决,若无问题,则再焊接其他部分,逐步扩展,直至完成整个实验板。实验板上电运行时,要经常察看各芯片的发热情况,当出现过热现象时要及时断电检查,并结合软件检查是否出现短路和虚焊问题。