增强的CMOS电荷泵和相频检测器设计

在当代无线收发器中,频率合成器掌控频率变换。合成器的性能(主要是其相位抖动和杂散输出幅度)将在很大程度上决定整个无线系统的性能。许多因素影响相位抖动和杂散输出,这些因素包括:合成器架构的选择(整数N或分数N锁相环)、环的数量及比较频率等。合成器一般包括:一个压控振荡器(VCO)、前置分频器、可编程除法器、数字控制逻辑电路、相位-频率(相频)检测器(PFD)、电荷泵(CP)和环滤波器。专注合成器的两个关键部件——PFD和CP,可改进合成器的相位抖动和杂散输出指标。

典型情况,一个PFD有两个输入和输出。一个PFD一般包含两个D型触发器(DFF)及复位逻辑电路。输入之一用作参考频率信号,另一个用作分割后的VCO信号;在PFD中,对这两个输入信号的相位差进行比较。若产生相位差,则会在PFD的UP或DOWN输出端生成一个脉冲。理想情况是,该脉冲宽度应与该相位差呈比例关系。

CP包括一个电流阱(current sink)、一个电流源以及其它相应的开关网络。UP/DOWN脉冲控制CP向环滤波器提供或从环滤波器吸收电流的时间长短。图1显示的是典型PFD和CP电路。若电流源是用PMOS实现的,则要插入一个反向器来确保极性正确。

假定开始时,f1和 f2为零,则可容易地理解电路的工作机理。f1时钟的跳变将把DFF的上面部分触发为逻辑高态。此时电流源会将电流注入环滤波器。当f2输入发生时钟跳变时,DOWN输出将成为逻辑高态。与非门(NAND)是复位电路,它生成一个逻辑低将两个DFF复位。电流源被关断,并产生一个对应于f1和f2相位差的脉冲。对f1领先f2的情况,则如上述描述的逻辑;当f1落后 f2时,发生一个类似过程,它在DOWN通路生成一个脉冲,并开启NMOS以吸纳来自环滤波器的电流。

传统PFD的最常规实现是采用标准逻辑核(图2)。在此情况,元件U2和U3形成DFF的上半部分,而U4和U5组成DFF的下半部分。四输入与非门生成复位信号。电路的其余部分包括缓存/延迟单元(为处理死区问题)和极性反转缓存器。这是一种常用的坚固结构,虽然复位通路逻辑门的传播延迟限制了该结构的速度。另外,其频率检测性能也并没被进行优化处理。为了该PFD能钳位VCO的最高控制电压,F1必须比F2快10倍。

简单是获得更快合成器速度的关键。通过采用类似真实单一相位时钟(TSPC)这样的更快更简单的逻辑,只需几只晶体管而非几个逻辑门就可实现DFF。图3显示的是该方法的一个通用实现。晶体管M1到M9形成上部锁存器,M11到M19形成下部锁存器;这两个锁存器相等。场效应晶体管(FET)M1到M6基本上表述了一个利用预充电技术的修改了的标准双n-CMOS锁存器。

该锁存器的工作原理简单明了。节点A被预充电至逻辑高态。当f1从低态跳变为高态,而f2仍为低态时,晶体管M5导通且M5开启由M4和M6形成的反向器。节点B被拉低。晶体管M7和M8形成一个反向器以生成UP信号。为解决该架构的一个特殊问题,增加了晶体管M9。因上和下部锁存器的延迟一般不匹配,这样,即使在没有输入相位差时,锁存器间的差异也会在UP和DOWN输出上生成一个窄脉冲。节点A通过M9放电至地(GND)。随着f1从低变为高,节点B被拉至逻辑高态(H),而UP输出将被拉至逻辑低(L)态。底部锁存器以相同方式工作。

与传统PFD相比,在图3所示的简单方法中,不要求反馈复位逻辑电路。复位延迟很短,利用TSPC实现的PFD具有比传统PFD实现方式高得多的工作频率;许多研究报告说,简单方式的工作频率可达几GHz。虽然本文仅简单涉及了TSPC的实现,但它是一个非常灵活的逻辑系列、具有许多可能的变化。

与图3比,图4显示了用于PFD的TSPC的另一种实现。图4中的锁存器以下述方式工作。设开始时,复位和f1为逻辑低态,晶体管M1和M2导通。M3的漏极被预充电至高态。f1的上升沿将使晶体管M5导通。因M3的漏极被预充电至高态,M4的漏极将处在低态。它然后被反向以生成UP信号。底部锁存器与上部锁存器相同。因两个锁存器生成所需逻辑输出的反转,所以用一个或非门(NOR)取代与非门。与图3所示的电路比,图4所示的电路更接近传统的PFD架构。图4和图3电路的主要区别是如何生成复位信号。

|

|

可增加两个DFF以改进频率驳合(pull-in)速度。它们帮助在即使f2仅是f1频率的两倍时,也能钳位控制电压。图5显示的是该增强方法的典型实现,它也需要两个额外的“或”门。

在PFD设计中,克服“死区”是个熟知的问题。对一个理想的PFD来说,在输入相位范围从–2p到+2p以及斜率等于PFD的增益时,可将相位响应看作是通过原点的线移动。对一款不那么理想的PFD来说,存在一个没有增益的死区,从而使靠近原点附近的线的斜率趋向平坦。在死区,合成器会短暂失(去)锁(相功能)。相位噪声将累加,直到其大得可在死区外存在,而且相位抖动指标将恶化。

死区来源于CP内开关有限的导通/截止时间和开关充/放电环滤波电容所需的时间。因f1和 f2在频率上很接近,所以,导通和截止脉冲变窄。若CP开关的不足够快,则在CP可对环滤波充/放电前,DFF甚至就可能复位。解决方案之一是在复位通路特意增加延迟。为避免死区,延迟必须足够长;为满足较高工作频率要求,延迟还需足够短。

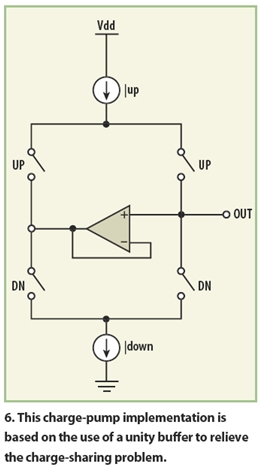

在来自环滤波器的输出容抗和通过电流源(C1)/阱(C2)的寄生容抗间的电荷分配是个问题。当PLL被锁闭时,CP关闭。CP的输出管脚与漏极电压(Vdd)和GND绝缘。当CP导通时,随着PLL接近锁固态,两个开关都导通。电容C1将从Vdd放电至输出电压Vout,电容C2将从GND充电至Vout。环滤波器电容必须对任意压差提供补偿。此举会在控制电压上产生纹波,它看起来象是合成器输出频谱的杂散产物。图6提供了克服充电-分配问题的一种方式——增加一个一体缓冲器。该一体缓冲器的输出同时接至电流阱和电流源输出节点。这将使两者一直都保持相同的电压值Vout。

|

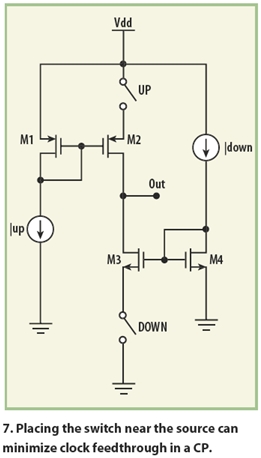

当设计一款优良的CP时,电荷注入是另一个需考虑的问题,当电流源/阱开关导通时,在晶体管栅极下面积聚着电荷。当这两个开关关断时,栅极下面的电荷将注入晶体管的漏极和源极。因开关紧邻输出管脚,注入的电荷将在输出产生纹波。时钟贯通(feedthrough)机制是通过由栅极到漏极和栅极到源极间产生的寄生电容(Cgd)和(Cgs)的时钟泄漏。解决方案之一是在远离输出节点的地方放置开关,或在源极安放开关(图7)。这些措施将减小电荷注入和时钟贯通效应。

电流阱和电流源间的不匹配是输出纹波的另一个元凶。当PLL锁固时,网络(net)电流应为零。因电流的不匹配,PLL必须刻意地生成一个相位差来降低网络电流,但这又会在频率输出上被看成伪信号。解决方案之一是在电流源/阱设计中仅采用NMOS(图8)。在该方法中,晶体管M5和M6形成电流镜。晶体管M1和M2负责设置UP电流。当UP节点为高时,偏置电流通过M1流动。当UP节点为低时,偏置电流通过M1流动。晶体管M3和M4负责操控DOWN电流脉冲。该方法带来的额外好处是通过操控该偏置电流带来的更快的开关速度,但代价是更大的功耗,因在不使用时,偏置电流并不关闭。

控制合成器相位噪声并非简单地借助数字信号处理(DSP)技术或采用特殊的具有最低噪声指标的VCO就万事大吉了。实际上,为降低相位抖动及杂散响应,必须仔细设计PFD和CP。通过遵循前面讲述的指导原则,可显著改善PLL合成器的相位噪声。