基于Avalon总线的VGA图像控制器的实现

摘要:本文介绍了Avalon总线的基本概念和VGA图像控制器,着重描述了VGA图像控制器的设计,并利用Quartus II软件和SOPC Builder实现了VGA图像控制器,在DE2开发板上进行了仿真验证,证明了该设计方法增加了系统的灵活性,简化了设计。

关键词:Avalon总线;VGA;VHDL;Nios;SOPC

引言

利用可编程片上系统SOPC( System on Programmable Chip)可以实现VGA图像控制器在工业现场中的许多实际应用。以硬件描述语言VHDL对可编程器件进行功能模块设计、仿真综合,可实现VGA显示控制器显示各种图形、图像、文字,并实现动画效果。

在SOPC设计中,比较重要的是将自己设计的IP核或购买的第三方IP核组合在一起,这需要借助一定的规程在片上总线中进行数据交换。Avalon总线配合Nios软核,可以像搭积木一样将用户设计的IP核以及第三方提供的IP核捆绑在一起,在Nios软核的统一调度下,满足多种应用场合的需要。本文基于Avalon总线的VGA图像控制器设计实例,将用户设计的VGA图像控制器通过Avalon总线作为Nios软核嵌入式处理器的一个外设,可控制显示多种图形、图像、文字,并可实现动画效果,具有一定的实用价值。

Avalon总线概述

Avalon交换式总线是用于系统处理器和外设之间的内联总线,由SOPC Builder系统设计工具自动生成,构建在Nios软核嵌入式处理器上。

基本的Avalon总线传输是在主设备和从设备之间传输一个字节、半字或字。一次传输过后,总线可以立刻进行下一次传输,而且与上一次传输的目的设备和源设备无关。Avalon总线还支持外设等待执行时间、传输外设和多主设备总线等功能。这些传输模式使得在一次总线传输中,在外设之间能够完成多个数据单位的交换。

Avalon总线支持多个总线主外设,任何一个主外设都可以进行直接存储器访问(DMA),而无需Nios软核处理器干预。一般的系统总线采用主端仲裁机制,而Avalon总线DMA的从方仲裁机制,能够实现多模块并行DMA。该总线使用极少的逻辑资源支持数据总线的复用、地址译码、等待周期的产生、外设的地址对齐、中断优先级的指定,以及高级的交换式总线传输。

由于Avalon总线的开放性,用户的任何运算逻辑单元,只要加上必要的数据交换接口,即可通过该总线与Nios软核嵌入式处理器对接。它还为用户提供了非常友好的接口,使得系统搭建中的一些细节问题得到屏蔽,大大减轻了系统搭建的工作量。

VGA接口及设计参数

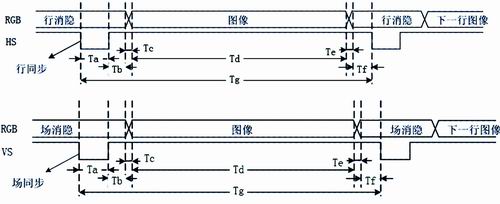

常见的彩色显示器一般由CRT(阴极射线管)构成,彩色由R(红)、G(绿)、B(蓝)三基色组成,用逐行扫描方式进行图像显示。阴极射线枪发出的电子束打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素,由于三基色的每个信号都有高低两种电平,因此共可显示8种颜色,其颜色编码如表1所示。显示器扫描从屏幕左上方开始,按从左到右、从上到下的顺序进行扫描。每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐。每行结束时,用行同步信号进行行同步;所有行扫描结束,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。对于普通的VGA显示器,其引出线共含五个信号R、G、B三基色信号和HS行同步信号、VS场同步信号。对于VGA显示器的这5个信号的时序驱动,要严格遵循VGA工业标准,即640×480×60Hz模式。图1是VGA行扫描、场扫描的时序图,表2、表3分别列出了它们的时序参数。

图1 VGA行扫描、场扫描时序示意图

VGA工业标准显示模式要求行同步、场同步都为负极性,即同步脉冲要求是负脉冲。设计VGA图像控制器要注意两个问题:一个是时序驱动,这是完成设计的关键,时序稍有偏差,显示会不正常,甚至会损坏彩色显示器;另一个是VGA信号的电平驱动,对于一些VGA显示器,HS和VS的极性可正可负,在显示器内可自动转换为正极性逻辑。

当VS=0、HS=0时,CRT显示内容为亮的过程,即正向扫描约26ms。当一行扫描完毕,行同步HS=1,约需6ms;在此期间,CRT扫描产生消隐,电子束回到CRT左边下一行的起始位置(X=0,Y=1);当扫描完480行后,CRT的场同步VS=1,产生场同步信号时,扫描线回到CRT的第一行第一列(X=0,Y=0)处,时间约为两个行周期。

VGA图像控制器设计

流模式VGA图像控制器设计

对于信息量大的彩色图像显示,可将像素点数据存于FPGA内部EAB RAM、外部ROM或RAM中。标准VGA的画面大小是640×480,每秒需要扫描60个帧,像素时钟为25.175MHz,每一个点的扫描周期只有40ns左右。如果每个点都是Nios软件扫描产生,系统配置要求非常高,并且需占用大量CPU资源。因而可以使Nios CPU通过Avalon总线,利用DMA控制器在流模式VGA图像控制器和SRAM之间建立一条DMA传送通道,由硬件完成像素信息的自动读取,从而解决上述问题。这时,Nios CPU所要做的仅仅是完成SRAM中对应图像的更新。

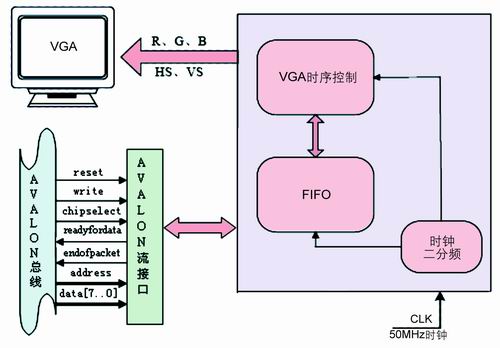

图2所示为Avalon流模式VGA图像控制器的硬件结构图。该控制器由3个部分构成:VGA时序控制器、FIFO存储器和Avalon流接口。其中,VGA时序控制器用来产生包括R、G、B、VS、HS等在内的五个VGA信号;FIFO存储器作为控制器的缓冲区,用来存储从SRAM送来的图像数据 。

图2 VGA图像控制器的硬件结构图

VGA图像控制器在SOPC Builder中的安装

Quartus II内集成了SOPC Builder,只要将设计好的Avalon流模式VGA图像控制器作为一个外设安装到SOPC Builder中,就可以在Nios系统中使用该图像控制器。

对于尚未集成SOPC Builder的功能模块,SOPC Builder提供了一个开放的接口。可以选择Interface to User Logic,给这个接口分配系统资源,然后在接口上加入用户逻辑就可以了。开发VGA图像控制器的关键是要符合Avalon总线规范规定的接口以及时序逻辑要求,以使SOPC Builder能够自动完成总线仲裁、总线宽度转换、地址译码等逻辑。本设计中, 由于工作于流模式的VGA图像控制器可以看成一个存储器,在Interface to User Logic对话框中,选择总线类型为Avalon Memory Slave。

控制器的仿真

在Verilog或VHDL的仿真文件生成之后,利用Quartus II对设计进行软硬件的协同仿真,以验证硬件逻辑的正确性。软件被编译成可执行的代码,然后在SOPC Builder生成仿真文件时被加入到RAM行为模型中去。Nios CPU行为模型调用RAM的程序,对系统运行时的行为进行仿真。

利用Quartus II 生成下载文件并下载

利用已有的集成开发环境,可以将上述网表和HDL的混合文件进行布局布线,生成最后的下载文件,并通过下载线下载到FPGA中去。本文使用的是USB接口,通过USB下载到DE2开发板中 。

结语

本文介绍了一种VGA图像控制器的设计方法,并通过实例阐述SOPC的搭建过程,可以看到SOPC技术由于采用了片上总线技术,增加了系统的灵活性,很好地简化了设计。■

参考文献

1. 潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2005

2. 潘松,黄继业.SOPC技术实用教程[M].北京:清华大学出版社,2005

3. 易青松,王卫源,戴紫彬.信息安全SOPC硬件平台的架构设计[J].单片机与嵌入式系统应用,2006,(12):10-12