基于DSP的语音数据采集卡设计与实现

摘要:本文给出了基于DSP的一款PCI接口的语音数据采集卡设计,不仅解决了传统语音数据采集卡存在的一些问题,而且能够对所有语音通道类型通过软件任意设置。本文结合软件设计,系统阐述了语音数据采集卡的功能和应用。

关键词:DSP;PCI;全双工通信;IVR

引言

随着计算机电话集成(CTI)技术的蓬勃发展,语音数据采集卡在电信增值服务、IVR系统、录音系统等领域有了广泛的应用。本文设计了一款基于DSP的语音数据采集卡,将模块集成到载板上,具有很高的市场价值。

系统的硬件架构

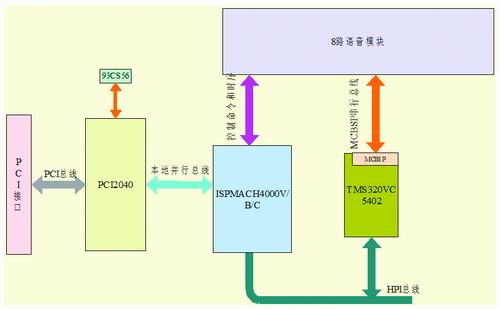

系统的硬件电路部分主要由DSP语音处理和交换电路、语音模块、PCI接口电路、CPLD控制命令和时序产生电路组成,如图1所示。

图1 硬件结构

DSP语音处理和交换电路

该电路是整个系统的核心,主要芯片TMS320VC5402主频可达100MHz,片上资源有40位ALU,17×17乘法器,4K×16位ROM,16K×16位SRAM,8位扩展主机接口(HPI)等。

VC5402的引脚大多数有内部的斯密特触发器以及上拉电阻,对于设计者来说外部电路设计相对简单,不用作特别的处理,但是中断源输入必须从外部接上拉电阻。

语音模块

语音模块是本系统的模拟电路部分,容易受到电磁干扰,使音质变差,在设计当中要注意PCB的布局布线,电阻电容的选取。

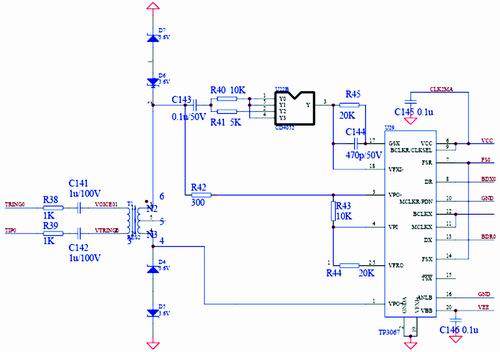

该模块实际上是语音CODEC电路,核心编解码芯片选用TP3067,完成语音的AD/DA转换。TP3067具有完整的话音到PCM和PCM到话音的A律压扩编解码功能。它的编码和解码工作既可同时进行,也可异步进行。

同步工作时,主时钟加到MCLKx端,移位时钟加到BCLKx端,主时钟的频率通过BCLKX\CLKSEL选择。如果BCLKx\CLKSEL=0,主时钟为1536kHz或1544kHz;如果BCLKx\CLKSEL=1,主时钟为2048kHz。移位时钟可以从64kHz到2048kHz,需和主时钟同步。在这种方式下,编解码主时钟和移位时钟相同。

异步工作时,MCLKx和BCLKx上均需2048kHz时钟,若要获得最佳性能,两者应该同步。同样,BCLYx和BCLKx\CLKSEL端也要加入编码和译码时钟,分别用作编码输出和译码输入PCM码流的移位时钟,两者均可以从64kHz到2048kHz。FSX和FSR分别为编码和解码的帧同步脉冲,FSX脉冲开始一次编码周期,并把上次编码的结果在BCLKx的上升沿从DX上移出,经过8次移位后,DX回到三态。FSR脉冲开始解码周期,PCM数据在BCLKR(同步方式中为BCLKx)的下降沿锁入接收寄存器,FSX和FSS的频率均为8kHz。

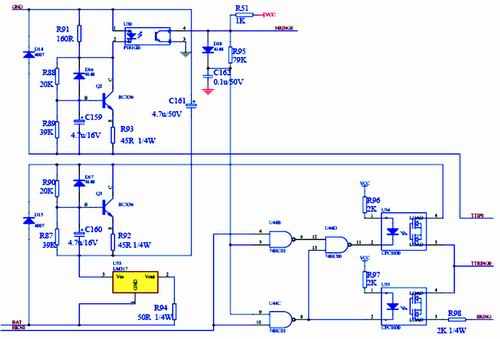

电话语音输入信号TRING0和TIP0通过设置进入语音模块。语音模块分成中继或者座席两种类型电路,可以由软件自由设置。中继和座席的后端编解码电路是相同的,如图2所示,而前端电路有明显的区别,如图3和图4所示。为了尽可能消除回波干扰,需要进行阻抗匹配,通过CD4052选择信号是经过R40的匹配中继前端电路通道,还是R41的匹配座席前端电路通道。

图2 一路语音模块后端编解码电路

图3 一路语音模块中继前端电路

图4 一路语音模块座席前端电路

PCI接口电路

DSP与主机的数据交互是PCI运算平台的设计关键。目前PCI接口卡的设计一般有两种方法。一种是将PCI接口完全集成到ASIC中,这样做的好处是集成度高,量产的生产成本低,但购买现成PCI控制器IP的价格昂贵。另一种方法是根据PCI协议在FPGA中实现PCI总线接口控制器,但由于PCI总线协议自身的复杂性,要在短期内做到操作稳定难度很大。因此,一般开发PCI接口卡的时候都使用现成的PCI接口芯片。

我们采用了目前较为通用的PCI2040,该芯片提供了一个从PCI总线到本地DSP芯片的无缝连接。

PCI2040工作时需要配置一片EEPROM,本设计中选用93CS56。93CS56会在PCI卡上电的时候配置PCI2040, 主要配置PCI卡的vendorID 和deviceID本地端空间的基地址和大小,以及每个空间的其他一些参数。

系统的软件设计

本文的板极软件包括CPLD设计,进行语音处理和交换的TMS320VC5402的DSP程序设计。

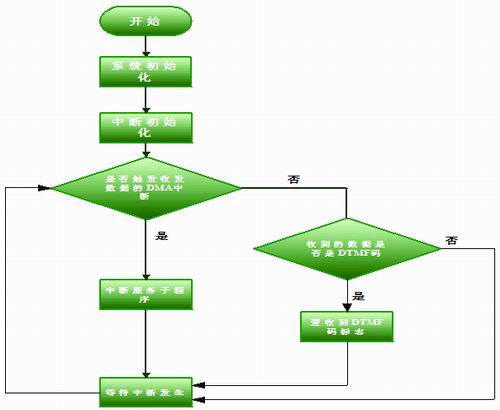

本文CPLD设计部分主要是产生语音模块需要的8kHz帧同步信号和2MHz的工作时钟,这两个信号均同步于一个本地的4MHz时钟,并同步于DSP芯片McBSP接口所需要的帧同步信号和工作时钟;DSP程序设计将PCI2040芯片的本地并行8位RAM总线转化为DSP芯片的HPI总线;当TMS320VC5402读取8路语音通道的线上电压采样数据时,把TMS320VC5402读外部RAM的控制信号转换为A/D芯片AD0820的控制信号,将采样数据放到TMS320VC5402外部RAM的数据总线上,完成采样数据的读取;在内部设置一些控制状态寄存器,对语音模块类型设置和状态进行检测。 TMS320VC5402主程序流程如图5所示。

图5 主程序流程

这里,值得注意的是DMA控制器的同步触发方式。接收数据时,DMA控制器的同步触发方式设置为由McBSP的接收事件(REVT)触发,即每收到一帧数据(32个字节)触发一次DMA控制器,将数据搬移到指定数据存储区。发送数据时,DMA控制器的同步触发方式设置为发送事件(XEVT)触发,即每发送一帧数据(32个字节)触发一次DMA控制器,将数据由存储区搬移到DMA的发送地址中。

整个TMS320VC5402的程序基本实现了语音数据采集卡的所有功能。

结语

本文在提出总体设计方案的基础上,完成了系统的硬件、板级软件设计及调试,经过长期的实际运行和验证,取得了满意的效果。

参考文献

1. TMS320VC5402 Fixed-Point Digital Signal Processor.http://www.ti.com.Texas Instruments,2000

2. Pci Local Bus Specification Revision 2.2 December 18,1998

3. 马磊,万旺根. PCI2040在DSP与PCI总线接口中的应用.电子技术,2001年第一期

4. 刘益成著. TMS320C54x DSP应用程序设计与开发. 北京航空航天大学出版社,2002年5月