基于Virtex-II的时钟数据恢复电路的设计

1.引言

由于通信对带宽的需求迅猛增长,促使一系列基于差分、源同步、CDR(Clock Data Recovery,时钟数据恢复)等先进技术的互联方式应运而生。在高速率的接口设计中,由于采用含有源同步的差分串行传输方式(如LVDS、LVPECL 等),传输过程中时钟和数据分别发送,各信号瞬时抖动不一致,从而破坏了接收数据与时钟之间的定时关系。时钟恢复就是在串行数据输入中引入数据比特率以产生某一相同的特定时钟频率。该时钟的相位由可在数据模式的中心进行数据采样的一个锁相环来确定。通常情况下,数据时钟的恢复电路是采用PLL(Phase Loop Lock,锁相环)来实现的,PLL 是相位和频率跟踪的最有效的方法之一,可直接应用于大规模系统中。但对突发信号来说,锁相环不能满足其快速同步的要求,大的相位变化就能引起失锁,而且再锁定需要的时间也较长。也有人采用全定制的过采样时钟恢复的方法,但这种基于多相位的数据采样和数字化后处理的方法需要用高于系统速率几倍的采样速率,然后通过相位比较选择最佳的采样,从而实现数据恢复。由于需要很高的采样速率,对于高速率的接收模块来说,工艺上很难得到实现。FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)在许多领域均有广泛的应用,特别是在通信领域,由于具有很好的实时性而使得信号的实时处理成为可能。基于Xilinx 公司Virtex-II系列FPGA,采用相位偏移的方法,等效的实现高于系统时钟的采样速率,从而实现对时钟数据信号的恢复。

2.设计原理

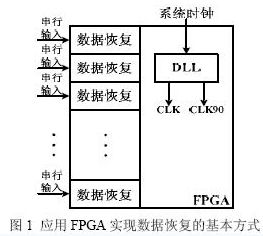

时钟数据恢复允许接收器将输入的数据流中的时钟或数据提取出来。通常,接收器从到来的数据流中提取数据,并将这些数据送到一个单独的时钟域中,然后把这些提取的数据送到FIFO 作进一步的处理。有时,接收器的时钟也用作数据的前向传输。数据恢复的速度受到DLL(Delay Locked Loop,延迟锁定环)所能接受的最大时钟的限制,典型的数据恢复的表示如图1 所示。

系统时钟输入到一个DLL 单元,如图1 所示。DLL 的CLK 为同步电路提供时钟,同时反馈回DLL。DLL 的另一个输出(即CLK90)延迟四分之一周期后与原时钟同步。Xilinx公司Virtex 系列FPGA 中提供了多个数字时钟管理器(DCM),DCM 模块可提供CLK 及CLK90 输出,其中CLK90 为CLK 相移90 度后的输出,两个输出是完全同步的,如下图2所示(DCM 其他端口省略)。

在数据时钟恢复时,将到来的数据分别输入到四个触发器,其中两个触发器由CLK 作为计数时钟(一个用CLK 的上升沿,一个用CLK 的下降沿),另外两个由CLK90 作为计数时钟(一个用CLK90 的上升沿,一个用CLK90 的下降沿),如下图3 所示。这里特别要注意:保证从输入引脚到四个触发器的延迟基本一致。要使延迟保持一致,可对设计的时钟网络设置MAXSKEW 参数[3]。

对于图3 数据时钟恢复电路存在如下的时序关系,如图4 所示。A、B、C、D 分别表示四个不同的采样点,输入数据1、2、3、4 分别表示四种不同的数据到来的情况。

图3 中的第一列触发器的触发分别由时钟CLK 的上升沿、时钟CLK90 的上升沿、时钟CLK 的下降沿及时钟CLK 的下降沿触发。按照这样的方式来触发就可以得到四个数据采样点,即图4 中所示的A、B、C、D 四个点。这样就将原始时钟周期分成了四个单独的90度的区域,在这里我们定义四个区域为四个不同的时钟域a、b、c、d。这样,如果系统时钟为200MHz,那么图3 所示的电路就相当于产生了800MHz 的采样速率。但是仅仅通过一阶的触发器,输出的采样数据存在亚稳态的问题,因此需对采样点作进一步的处理。这里可将四个采样点通过进一步的触发,除掉亚稳态的问题,从而使采样点移到下一个相同的时钟域。通常,亚稳态的去除要经过两三级的处理,这就使得在有效数据输出前会有数位无效的数据,但此时DCM 的locked 并未锁定,因此可由此信号来指示输出数据的有效性。在数据采样的第一个阶段,电路检测数据线上数据的传输。当检测到有数据传输时,对传输数据的有效性进行确认。确认数据有效后,输出高电平来指示采样点有数据传输。因为有四个输出,所以需要一个复用器来选择数据。复用器从选定的时钟域中选择数据位,例如检测电路确定从时钟域a 中采样的数据有效,那么将时钟域a 中采样的数据通过输出端输出。

3.FPGA 实现及仿真结果

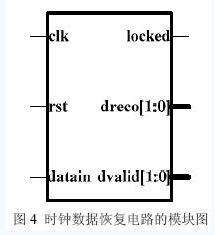

应用DCM 模块产生用于时钟数据恢复的CLK 及CLK90。设计的时钟数据恢复电路的模块如图4 所示。其中clk 为输入时钟,rst 为复位输入,datain 为输入待恢复的串行数据,locked 为DCM 锁定端,dreco[1:0]为恢复的时钟数据输出端,dvalid[1:0]指示输出恢复的时钟数据有效。dreco[1:0]分为高位和低位,dvalid[1:0]的高位和低位分别指示dreco[1:0]的高位和低位有效。

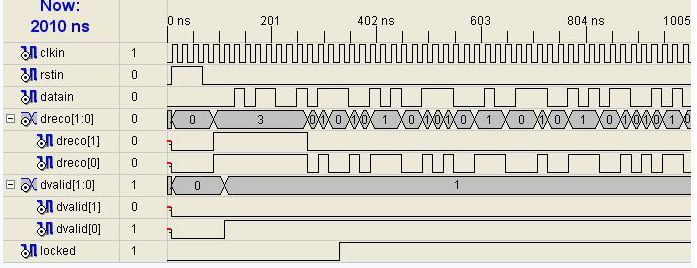

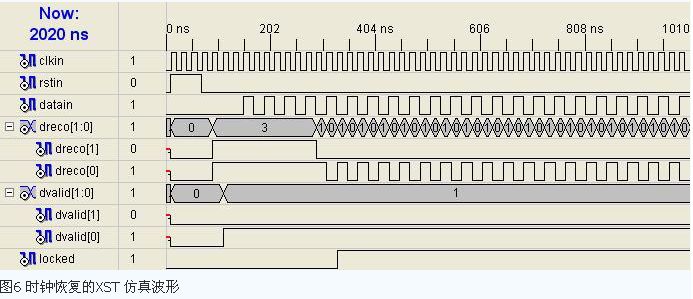

对所设计的时钟数据恢复电路应用ISE 软件内嵌的XST(Xilinx Synthesis Technology)综合工具进行综合,得到的数据及时钟恢复的仿真波形分别如图5 和图6 所示。

图5 数据恢复的XST 仿真波形

图6 时钟恢复的XST 仿真波形

从图5、图6 所示的对输入数据及时钟信号进行恢复的XST 仿真波形中可以看出,当dvalid[1:0]指示输出的时钟数据有效时并不是从指示有效的第一位开始就能正确恢复,而是需要经过一段时间(这段时间主要是由于存在的亚稳态造成的),经过这段时间,到DCM的locked 端输出高电平时,信号被锁定,此时输出的时钟数据开始正确恢复输入的时钟数据信号。

4.结论

从仿真结果来看,由于电路稳定需要一定的建立时间,因此输出数据流的前几位是无效的数据位。但当电路稳定下来后,DCM 锁定信号,此时可以有效地对输入的时钟数据进行恢复。同时,由于恢复速度受限于延迟锁定环(DLL)所能接受的最大时钟,因此该电路存在最大的可恢复数据的速率,通常情况下Virtex-II-5 器件所能恢复的最大数据传输速率为420Mb/s。