基于StarCore SC140的优化技术

摘要: StarCore SC140 是一款采用指令级并行(ILP)技术的DSP 内核, 本文从C 语言级和汇编代码级两方面探讨了其优化方法。关键词: DSP SC140 内核优化

随着DSP 技术的不断发展和完善, DSP 厂商纷纷推出了自己的高级语言编译器, 但编译器编译出的汇编代码在保证正确性的前提下很难兼顾效率。在一些实时性要求比较高的场合( 如音视频处理) 必须对某些关键的算法和代码进行优化。StarCore SC140 这款DSP 内核在体系结构、数据存取及运算上都与传统的TI 系列有明显的差异, 它可以在原来的基础上应用一些比较有对性的方法来大幅度提高程序优化效率。本文根据作者在SC140 上开发AACPlus_v2 音频解码器的经验, 着重从C 语言级和汇编代码级两方面探讨其优化方法。

1 StarCore SC140 体系结构

StarCore SC140 内核包含三类功能单元: 数据算术逻辑单元( DALU) 、地址生成单元( AGU) 和程序序列器单元( PSEQ) 。采用指令级并行技术(ILP), 共有6 个执行单元, 包括4 个ALU 和2 个AGU, 最多可以同时执行6 条指令, 而且支持SIMD。SC140 采用变长执行组( VLES) 模型, 执行过程以执行组为单位, 采用由指令预取、取址、指令分配、地址生成和执行组成的5 级流水线结构。SC140 采用单一的内存空间, 在内存和内核之间有两组数据总线和一组程序总线, 可以同时高速存取两组数据。

2 SC140 的优化技术

2 .1 Profile 分析

将高级语言程序代码用手工汇编优化固然可以降低MIPS 消耗, 但同时也会带来工作量的提高及出现改写错误。所以对程序进行Profile 分析, 找出消耗MIPS 比较集中的模块或函数进行手工汇编优化是十分必要的。以音频编码器AACPlus_v2 为例, 消耗MIPS 集中的函数, 即计算和循环集中的函数, 主要包括dit_fft (快速傅立叶变换)、cplxAnalysisQmfFiltering(分解QMF 滤波器)、cplxSynthesisQmfFiltering( 合成QMF 滤波器) 等。另外还有一些函数, 虽然占据MIPS 的比重较大, 但本身计算并不是很复杂, 只是包含很多的判断分支。这样的函数用SC140 手工汇编优化的效率很低, 可以考虑在程序算法上优化。

2 .2 C 语言级的优化

对既有的C 代码进行适当的调整与变换, 不仅可以提高编译效率, 也可以为进一步手工汇编优化铺平道路。循环通常是程序中MIPS 可以集中消耗的部分, 要真正做好循环优化, 必须要了解所用DSP 的体系结构和特点, 做到有的放矢。循环的优化有三类: 循环展开、循环合并和循环拆分, 其中循环展开是使用频率最高也是最有效的DSP 优化技巧。由于篇幅所限, 下面仅针对循

环展开来说明具体的优化方法。

循环展开就是在循环内部对循环体的内容进行重复, 从而减少循环次数。这样做首先减少了循环跳转的消耗; 其次可充分利用StarCore 的结构特点, 即4 个DALU 和2 个AGU 实现并行。当然, 这种优化方法需要

满足一定的前提条件:

(1)前后循环体之间不能存在依赖关系;

(2)数据排列要满足边界关系;

(3)每个循环体所需要的寄存器不大于DSP 可提供

的寄存器数;

(4)循环体的次数是展开因子的整数倍。

另外有两个问题需说明:

(1)针对SC140 进行循环展开, 通常取展开因子为4, 因为SC140 的4 个ALU 可以实现四条计算指令的并行;

(2)若要使用SIMD实现一条

指令多个数据存取, 就要把存取数据的初地址放到8B的边界上, 这也是根据SC140 的数据总线为64 位决定的。

2 .3 汇编代码级的优化

C 语言级的优化固然可以使编译器更有效率, 但在复杂操作下, 编译器无法代替人的统筹和分析, 生成的代码会存在明显的冗余。对于一些关键的操作, 仍然需要通过手工汇编优化提高其执行速度。

2 .3 .1 利用硬件方式优化程序

SC140 中可以通过修改状态寄存器来切换硬件的工作模式。一些常见的DSP 算法在这种硬件的支持下可以大大提高优化效率。

(1)fft 倒位序

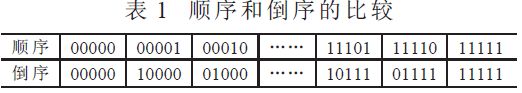

在数字信号处理过程中有一类与“ 顺序”相关的操作, 如快速傅立叶变换中常用的按时间抽取( dit - fft ) 算法等, 在程序中需要通过地址运算来实现。StarCoreSC140 针对这些运算提供了硬件寻址方式, 减少了程序中的地址操作。在数字信号处理中有大量的fft 运算, 以按时间抽取的基4 图基fft ( dit - tukey fft, radix 4) 为例, 时域倒序输入, 频域顺序输出。软件实现程序中有相应的倒序函数(一般是查表算法)来实现时域的倒序, 而将其移植到DSP上会发现这一部分非常耗时, 甚至与fft 本身的算法相差无几。正是在这样的前提下, SC140 提供了硬件上的倒序进位方式代替软件倒序算法, 提高了fft 的执行效率。其精髓就是将顺序存放的时间采样数据存入存储区内, 对该存储区使用SC140 反向进位寻址方式(reverse -carry addressing)。顺序和倒序的关系见表1 ( 以32 点fft为例) 。

因此, 只要对顺序存储的时间数据采用方向进位寻址, 就可以轻松实现倒序算法。还有一点值得注意, 在反进位的使用中, 如fft 的输入为2N 点, 数据宽度为2M 字节, 则分配的倒序存储区起始地址最低(N+M)位均为零,否则会引起寻址错误。反向进位寻址只要设置MCTL 寄存器中相应寄存器的状态位即可。

(2)环形存储

在实际应用中, 常常需要对缓冲区进行环形处理,即处理完数据后再从头数据继续处理。如果采用普通的处理方法, 则每次寻址都需用软件将所寻址地址与尾地址进行比较, 若超出范围, 则寻址至头地址。这样做将非常耗时。为此, StarCore 在硬件上支持环形缓冲区的管理。为了使用该功能, 需要将环形缓冲区分配到特定的存储空间。环形存储是通过设置MCTL 寄存器相应比特位的值实现的。

(3)Scale 模式的选择———用硬件完成移位操作

由于DSP 使用定点运算较多, 为了精度要求运算中会有大量Scale 调整, SC140 通过设置硬件的Scale 模式,在寄存器向内存存数据的同时完成移位。SC140 的Scale模式分为三种: ①Scale up: 左移一位后存入; ②Scaledown: 右移一位后存入; ③no Scale : 不移位直接存入。该模式通过设置SR 状态寄存器实现。

2 .3 .2 根据流水线实现并行处理

SC140 支持并行处理是该款DSP 内核的一大亮点,下面具体阐述如何运用并行处理提高优化效率。

(1)改变指令执行顺序

将相互不存在依赖关系的指令并行处理, 最大并行量为4 个ALU 操作和2 个AGU 操作。这是根据流水线实现并行优化方法的基础。当对某一寄存器同时进行读和写操作时, 虽然指令流水线中读和写同处于“ 执行”指令周期内, 而对时钟周期来说, 读操作先于写操作, 即遵循先读后写的原则。故对同一寄存器先读取后赋值的操作可以并行于同一指令周期内执行。

(2)多使用后加

根据指令执行周期可以看出, [sp + offset]取址模式需要耗费两个时钟周期, 在实际优化时应尽量少用, 而以对sp 进行后加直接取址。后加(post increment)取址模式是在对sp 直接取址后将指针移到sp +offset 的位置,只用一个指令周期即可实现。

(3)改变循环体的组合方式

如果遵循“ 读操作数- 〉计算- 〉存结果”的循环顺序进行, 则由于三个操作有很明显的依赖及先后关系, 使循环无法并行。若人为打乱这个顺序, 则执行效率会有很大改观:

①将第i 次循环结果储存; ② 计算第i+1 次循环的

结果; ③取第i+2 次循环的操作数。

此方法只用一个指令周期即可完成循环, 较优化前的三个指令周期优势明显。

(4)使用判断执行代替分支跳转

传统DSP 处理判断分支只能使用分支跳转指令, 而跳转由于预取指序列都将被重置而非常耗时, 尤其是在各个分支执行语句较少的情况下, 跳转的开销会显得更难以接受。SC140 的指令集中有判断执行指令IFT/IFF/IFA, 对小分支判断非常有效。在音频解码器的程序开发中, 采用了上述针对Star-Core SC140 的优化技巧和方法, 整个工程的MIPS 降低至优化前的16.4%。其中按时间抽取32 点基4 快速傅立叶变换函数dit_fft 完全采用汇编改写, 手工完成代码337 行, 平均执行指令周期由优化前的5 643 降到优化后的576, 取得了明显的效果。

参考文献

1 程佩青. 数字信号处理教程( 第二版) [M]. 北京: 清华大学

出版社, 2001

2 SC140 DSP Core Reference Manual[EB/OL].www.motorola.

corn/sps/dsp, 2001

3 SC100 C Compiler User′s Manual[EB/OL].www.metroworks.

com, 2000

相关推荐

在线研讨会

焦点