深空测距中可变带宽超窄带锁相环设计

1 引 言

在深空探测中,无论是深空飞行器跟踪、导弹跟踪、人造地球卫星轨道的测定等航天应用,都离不开距离的测量,所以测距具有很重要的作用。应用最多的连续波测距技术是侧音测距,伪码(PN)测距,以及两者的结合。又以侧音测距具有捕获时间短,设备较简单等优点而在目前航天测控中应用较广泛。因航天器发射功率小、通信距离远,收到侧音测距信号极微弱,考虑到信号有多普勒频移及振荡器产生的频率漂移,接收机的中频通带必须够宽。普通接收技术对此极低信噪比的测距信号无能为力,可以通过超窄带锁相技术来提高对微弱测距信号的检测能力。当输入信号强度低到 -180 dBW以下,为了提高锁相环路的输出信噪比,要求环路带宽非常窄,甚至要压低到1 Hz以下,才能满足性能要求。而使用这样小的环路带宽,又会在有多普勒干扰情况下,表现出锁定时间长、容易假锁、失锁等不良性能。这样就需要整个锁相环路带宽在一定范围可以变化:先使用比较大的带宽进行锁定以缩短锁定时间,再使用小带宽来提高锁定精度,以适应微弱信号输入锁相环在锁定时间与锁定精度两方面的需求。

本文提出了一种数字锁相环的基本原理和环路结构。对变带宽超窄带数字锁相环进行了数学建模与matlab仿真,结果表明:取环路带宽为0.1 Hz,当输入信号信噪比为-20 dB、环路锁定后的输入输出信号相位差小于2.8°;取环路带宽从10~1 Hz可变,输入信号信噪比为-5 dB、频偏10 Hz情况下,环路能够快速锁定(与带宽2 Hz环路相比),环路锁定后输入输出信号相位差小于1.7°。应用EDA技术设计了该锁相环电路,用FPGA予以实现。

2设计原理

2.1数字锁相环原理

传统模拟锁相环设计中关心的参数ω,ξ等通过电容、电阻、压控振荡器等参数实现,因模拟器件自身的局限限制了带宽的范围,而且模拟电路还存在直流零点漂移、难以调试等缺点。在数字锁相环设计中这些参数的设定就方便许多,精度也大大提高。

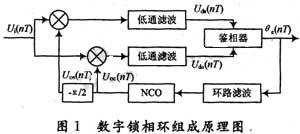

锁相环主要由VCO(压控振荡器,数字实现时为NCO(数控振荡器)、LPF(低通滤波器)、PD(鉴相器)及LF(环路滤波器)组成。数字环路原理图见图1。

2.1.1 锁相环数字鉴相器

输人信号与数控振荡器产生的两路正交信号相乘,通过低通滤波后,得到差频信号,然后求反正切可以得到相位差信号,完成鉴相功能。

2.1.2环路滤波器

数字锁相环设计中关键一点就是如何设计环路滤波器。环路滤波器用于衰减由于输入信号噪声引起的快速变化的相位误差和平滑鉴相器泄漏的高频分量,以便在其输出端对原始信号进行精确的估计。环路滤波器的阶数和噪声带宽决定了环路滤波器对信号的动态响应。

设计基于比例积分(PI)控制的数字环路滤波器。将鉴相器输出的相位误差信号经积分环节和比例环节调节后,分别产生积分控制参数以及比例控制参数,取这两个控制参数之和作为数控振荡器的控制参数,其结构如图2所示。

数字环路滤波器的设计与模拟环路滤波器相对应,仍存在区别,以二阶锁相环环路滤波器为例,模拟有源比例积分滤波器只能逼近理想积分滤波器的特性,而数字环路滤波器则直接根据理想滤波器进行等效匹配,推导如下。

理想积分滤波器的传递函数为:

![]()

利用双线形变化,得到数字环路滤波器的传递函数:

![]()

其中C1是比例系数,C2是积分系数,T是相干积分时间,对应到FPGA中为NCO的相位校正间隔时间。

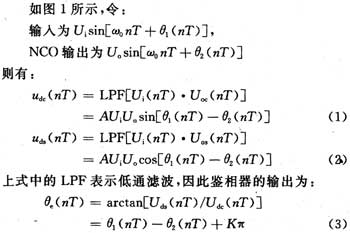

由文献1的推导,可以得到数字二阶环路滤波器的系数分别为:

其中,公式内各个参数的具体含义和计算公式是:ωn=8ξBL/(4ξ+1),ξ拿取0.707,Kd是鉴相器增益。NCO的控制灵敏度为K0,T为NCO更新时间。

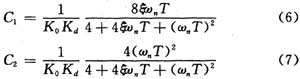

2.1.3数控振荡器

可见两种信号具有极其类似的表达形式,因此数控振荡器NCO可以借用压控振荡器VCO的有关概念。

2.2变带宽门限设置原理

输入信号极微弱的条件下,要求锁相环环路噪声带宽尽量压窄,可以提高锁定精度,带来的影响是锁定时间较长、在存在多普勒频偏的情况下易失锁。为在锁定时间、锁定精度、失锁概率中寻求一个平衡,要求所设计锁相环的环路带宽在一定范围可变化,如从十几Hz到零点几Hz。在环路开始工作时,使用较大带宽,可加快捕获速度;在捕获到信号之后,可换较小带宽,减小NCO输出信号的相位抖动、提高锁定精度。

要改变环路带宽大小只需要改变成对应的系数即可,在FPGA设计中这一点不难做到。所以变带宽锁相环的设计关键是变带宽的条件,即变带宽门限的设置。

由文献[2]可以知道,NCO输出信号相位抖动直接受到环路带宽和输入信噪比的影响,其关系如下:

![]()

式中σ2φ是由采用乘法器鉴相的锁相环路结构推导出的,在采用反正切鉴相器结构的锁相环路中应该为σφ。BI是环前的中频带宽,有进一步的推导:

![]()

通过公式推导可看出:给定不同信噪比的输入信号、不同大小环路带宽的条件下,可事先计算或仿真锁定之后输出信号的相位方差。以该数据为标准,与通过 FPGA方差统计模块测量得到的实际锁相环电路输出信号的相位方差作比较,可作为衡量环路是否稳定锁定的标准,进而作为变带宽的门限。

在实际应用时,配合输入信噪比估计值进行带宽变换。如果没有输入信噪比估计电路,就用最恶劣情况下输入信噪比进行计算或者测试。电路工作时,方差统计模块实时统计输出信号方差,当方差稳定小于当前环路带宽稳定锁定门限时,可通过变换参数将带宽压窄;如方差大于当前门限,可以认为环路失锁,可将带宽变大以再次锁定。

3锁相环仿真分析

通过matlab建立锁相环模型,通过改变比例系数与积分系数来变换环路带宽,再输入不同信噪比、频偏的信号,来衡量环路工作性能。

环路滤波器的两个主要参数:比例参数与积分参数可以通过式(6)、式(7)计算得到。具体设定为:锁相环路的DDS更新速率为68 kHz,即T=1.47×10-5。环路带宽BL变化范围为10~0.1 Hz。环路增益结合FPGA设计实际计算为2-5。

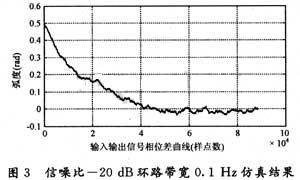

图3给出了输入信号初始相差30°、未加频偏、信噪比为-20 dB,锁相环环路带宽为0.1 Hz的仿真结果。这时所采用的比例系数为2-14,积分系数为2-33。仿真显示,需要5万点环路进入稳定锁定状态,主要是因为环路滤波器系数很小,锁定时间相对较长。

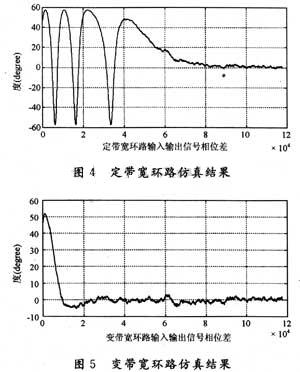

图4、图5所示是输入信号加10 Hz频偏、信噪比-5 dB条件下,带宽固定为2 Hz环路与变带宽(10~1 Hz)环路仿真对比图。从图中可以看出定带宽环路经过多次跳周后才锁定输入信号,变带宽环路一开始用较大带宽迅速将输入信号捕获,再用较小带宽提高锁定精度。变带宽的锁定速度快于定带宽,而且锁定后相位差基本一致。可见变带宽策略在很大程度上解决了捕获时间与锁定精度之间矛盾。

4 FPGA设计

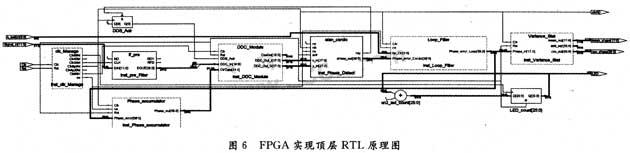

在Matlab进行模型仿真的基础上,进一步在FPGA平台上实现数字锁相环。FPGA芯片为XC4VLX100-4,开发环境为ISE 8.2,综合工具为Synplicity 8.1,仿真工具为ModelSim 6.1b。在XC4VLX100-4芯片上实现后所用资源为slice资源45%,LUTs资源33%。

图6为FPGA平台实现后顶层RTL原理图。

5结 语

深空测距中因其输入信号微弱,具有多普勒频偏等特点,这就要求锁相环带宽在一定范围可变的前提下尽量压窄。本文首先介绍数字锁相环结构为建立Matlab模型打下基础,再通过公式计算与模型仿真得到带宽低至0.1 Hz环路的系数,同时为克服超窄带锁相环锁定时间长的缺陷,设计可变带宽环路以加快锁定速度,最后通过仿真验证。

在实际设计中,整个环路主要考虑实现超窄以提高对弱测距信号提取能力,故变带宽范围比较有限。为应付更大范围多普勒频偏,需要外部电路对NCO进行频率引导或添加锁频环电路。