基于Q-Coder算术编码器的IP核设计

1 概述

JPEG2000[1,2]是新的静止图像压缩标准,它具有的多种特性使得它有着广泛的应用前景。目前为止,JPEG2000的解决方案比较少,并且其中的绝大部分是软件解决方案:Jasper[3]软件是经IEC JTC1/SC29/WG1小组推荐使用的实现JPEG2000的为数不多的软件之一。

由于软件实现JPEG2000的时间开销比较大,因此,JPEG2000编码系统很难应用于实际系统中;硬件解决方案由于处理速度大大提高,因而用硬件实现JPEG2000具有广泛的市场前景。但是,JPEG2000算法复杂,完全用硬件实现比较困难;然而使用硬件实现JPEG2000中的某些模块,相对而言就比较容易实现,同时也能大大提高编码效率。

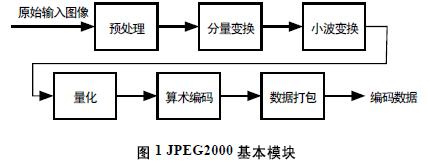

图1为JPEG2000的几个基本模块。文献[4]指出,软件处理中,图1中的算术编码模块的时间开销占据了整个软件时间开销的40%左右,若使用硬件实现算术编码模块必然能大大提高编码速度,对于提高JPEG2000的编码速度有着重要的意义。

2 Q-Coder算术编码器原理

Q-coder算术编码是一种特殊的高效自适应二进制算术编码器。其输入是成对待编码数据D(DATA)以及上下文CX(CONTEXT),数据D和上下文CX是由比特平台(bit plane)[1]产生的;输出则是压缩数据CD(COMPRESSED DATA)。在JPEG2000中,上下文指D周围8个相邻比特的状态,这些状态被特定的规则划分为19类,称为19种上下文。每种上下文都包含两部分内容,一部分选择了对数据D编码时使用的概率估计值对应的索引,另一部分决定了当前大概率符号所代表的符号,这两部分内容将在编码后被更新。

2.1 区间的递归划分

概率区间的递归划分是二进制算术编码的基础。每执行一次二元判定,当前概率区间就被划分成为两个子区间,并在必要的时候修改输出码流,使之指向该符号所在的概率子区间的下界。

在区间划分时,小概率符号的子区间和大概率符号的子区间这样排序:通常取靠近0的区间作为MPS的子区间,因此,若编码的是MPS,则应向输出码流中加入LPS子区间的长度。这种约定要求把编码的符号区别为LPS或MPS,而不是0或者1。因此在对一次二元判定编码时,必须知道该判定的LPS子区间的长度和MPS的含义。

2.2 编码约定和近似计算

Q-coder算术编码器设置两个寄存器:一个是概率区间宽度寄存器A,用于存放子区间的宽度,另一个是码字寄存器C,用来表示概率区间的下限。编码过程使用固定精度的整数运算和小数的整型表示形式,即X‘8000’代表十进制小数0.75。概率区间A的范围是,并且当A的整型值小于X‘8000’时,把A翻倍,即把A限制在十进制范围0.75–1.5之间,这个“翻倍”过程称为重整化。当A进行重整化时,C也必须同时翻倍。为了防止寄存器C发生上溢,每隔一段时间,应将寄存器C的高位部分移出并送至另外的寄存器中。

将A限制在十进制范围0.75~1.5之间,概率区间的划分可以使用简单的算术近似方法。如果LPS当前的概率估计值是,则子区间的精确计算如下进行:

3 算术编码器的实现

3.1 算术编码流程

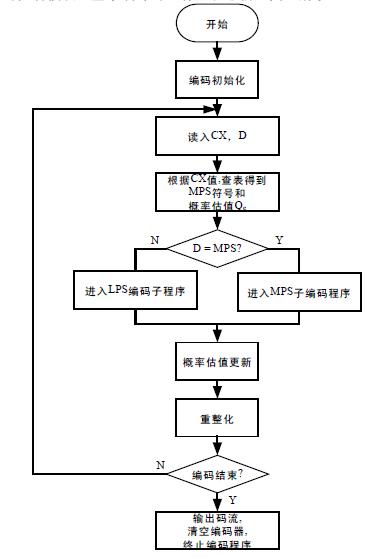

所有的设计都是用Verilog硬件描述语言编写的,由上述描述可知,算术编码器的输出不仅和当前状态有关,而且和输入也相关,所以本文选择Mearly有限状态机[5]来描述复杂的控制模块。整个设计的主有限状态机如图2所示。

图2 算术编码主有限状态机

3.2 模块设计

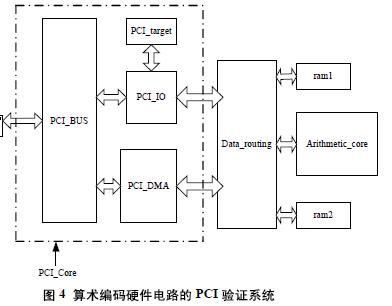

duram是双口sram作为片内存储单元存储输入的数据,当采用FPGA进行验证时,直接调用Altera公司的宏功能块即可;ari_core是实现算术编码的运算处理单元,包含一个存储概率估值和当前MPS符号的表以及LPS和MPS编码子程序;模块control是数据流控制单元,用于组织片内存储单元duram和运算处理单元ari_core以及片外sram的数据交换。模块control是整个设计的控制单元,负责调度以上各个模块,产生控制和联络信号以及地址信号。模块结构原理如图3所示。

3.3 电路验证

将布局布线后生成的文件下载到自行设计的一块FPGA的PCI开发板里进行验证,如图4所示。板上是一片Altera cyclone系列FPGA ep1c12qfp240,该FPGA含有约25万逻辑门、30KB内部RAM。PCI接口控制逻辑也是在FPGA中实现[6~8],然后编写PCI驱动程序和应用程序,先由Jasper软件处理,抽取软件中量化模块处理后的数据,输入FPGA中进行处理,再将数据返回给软件中的下一模块,验证本文设计的算术编码IP核的正确性,并计算处理时间。

4 实验结果与分析

(1)将Verilog源程序在QuartusⅡ软件中综合后,得到的参数如下:

1)器件名称:EP20K200efc484-2x;

2)FPGA时钟最高频率:45.18MHz;

3)Total logic elements:3660/8320 (44%)。

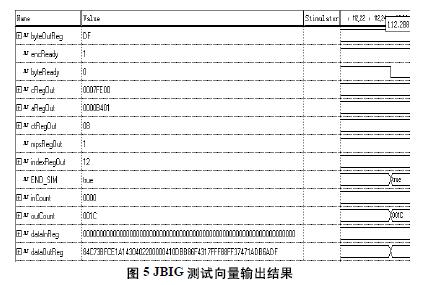

(2)功能验证。目前,只有JBIG[8]标准中有验证算术编码器编码正确性的测试向量,因此该测试向量被用以测试本文设计IP核的正确性。需要说明的是:JBIG标准中的算术编码器会产生“FF AC”标志位[8],而JPEG2000中的MQ-Coder算术编码器并不产生该标志位[1]。

将JBIG中的测试向量作为输入,经过本文设计的算术编码IP核处理后的结果如图5所示,由图5可知本文设计的算术编码IP核完全正确。

(3)由概述可知,Jasper软件具有一定的权威性,因此在实验中被使用。表1列出了对于同一个图像文件,Jasper软件中算术编码模块执行所需的时间和本文设计的算术编码IP核执行所需的时间以及两者时间之比。

5 结论

本文提出的一种实现算术编码的集成电路IP核,经过仿真和FPGA验证,能够符合JPEG2000标准,仿真结果表明,在相同的条件下,该IP核编码所需时间仅约为软件编码所需时间的40%,从而大大提高了算术编码的效率,使得将来其应用于实时处理系统成为可能;并且将来可以定制所需的ASIC电路,用于新一代数字照相机等具有广泛市场前景的 项目。

参考文献

1 Boliek M, Christopoulos C, Majani E. ISO/IEC JTC1/SC29/WG1 N1646R-2000 JPEG2000 PartI Final Committee Draft (Version 1.0)[S]. 2000.

2 张晓娣, 刘贵忠, 曾召华等. JPEG2000图像压缩编码系统及其关键技术[J]. 数字电视与数字视频, 2001, (8).

3 Jasper Project Home Page[Z]. http://www.ece.ubc.ca/~mdadams/jas per.

4 Adams M D, Kossentini F. JasPer: A Software-based JPEG-2000 Codec Implementation[C]. Proc. of Int’l Conf. on Image Processing, 2000: 53-56.

5 陈雪松, 藤立中. VHDL入门与应用[M]. 北京: 人民邮电出版社, 2000.

6 陈文正, 曹 明. PCI总线协议的FPGA实现及驱动设计[J]. 电子技术应用, 2003, 29(7): 15-17.

7 胡和平, 田宜波. 基于FPGA的PCI接口设计[J]. 计算机工程, 2003, 29(8): 156-157.

8 刘海平, 朱仲英. 基于FPGA的PCI总线接口设计[J]. 微型电脑应用, 2003, 19(9): 49-51.

9 JBIG Committee. ISO/IEC JTC 1/SC 29/WG 1 N1359-1999 14492 FCD[S]. 1999-07.