CMOS图像传感器IBIS5-B-1300的驱动时序设计

CMOS图像传感器产生于20世纪80年代,由于当时CMOS工艺的制造技术不高,以至于传感器在应用中的杂讯较大,商品化的进程一直很慢。至今,随着工艺的不断提高,CMOS图像传感器的应用范围也不断扩大,涉及到数码产品、通讯、工业,医疗等各领域。与CCD相比,CMOS图像传感器具有体积小,功耗低,成本低等特点。Cypress公司的CMOS图像传感器IBIS5-B-1300是一款高性能、大动态范围的图像传感器。图像传感器的正常工作需要有正确的驱动时序信号,本文就图像传感器IBIS5-B-1300,给出采用VHDL语言设计的驱动时序和仿真结果。

1 IBIS5-B-1300图像传感器

1.1 芯片简介

Cypress公司的IBIS5-B-1300将模拟图像获取、数字化和数字信号处理的功能集成在单一芯片中,是一款高性能的CMOS图像传感器。这款130万像素(1 280×1 024)的图像传感器可以采用SXGA或VGA格式输出,帧频可达27.5 f/s(1 280×1 024)或106 f/s(640×480)。

其主要特点如下:

(1)6.7μm的高填充因子像素单元。它可使器件的灵敏度较高,噪声较小。

(2)高的动态范围(单斜率积分下为64 dB)。当采用双斜率积分或多斜率积分时,动态范围可进一步提高。

(3)片载可调整增益和偏置的输出放大器。它能使信号的抖动限制在片载10 b ADC的输入范围之内。

(4)片载40 MHz的10 b ADC。它可直接对输出模拟信号进行模/数转换,该ADC在电气上与图像传感器分离,如果需要,可选择不经模/数转换而直接输出模拟信号。

(5)随机开窗模式和亚采样模式。随机开窗模式可以只对感兴趣的区域进行读出;亚采样模式可以很好地满足图像压缩的需要。

(6)片载时序与控制逻辑序列发生器、内部寄存器。它可使得设计者用较少的信号来控制传感器的工作。

1.2 工作原理

IBIS5-B-1300内部有12个寄存器,提供传感器工作所需的参数及工作方式。对寄存器写入的数据决定了传感器的工作状态。寄存器的数据写入接口有3种:并行接口、串行三线接口、串行两线接口。可通过芯片的IF_MODE和SER_MODE管脚接不同的值来选择不同的数据接口模式(如表1所示)。

并行接口使用16 b并行输入来载入新的寄存器值。串行3线接口(或串转并接口)使用串行接口将数据移入寄存器缓冲器,当完整的数据字移入寄存器缓冲器时,数据字才被载入当前正在编码的寄存器。串行2线是一个单向的接口,本文暂不做分析。

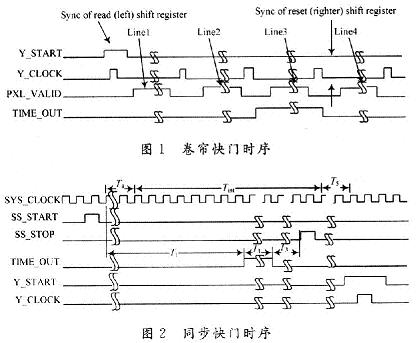

IBIS5-B-1300具有两种快门方式:卷帘快门和同步快门,用寄存器(0000)的bitO进行设定,“1”为卷帘快门,“0”为同步快门。时序如图1,图2所示。

在卷帘快门模式下,帧频Frame period=(Nr.Lines×(RBT+Pixel Period*Nr.Pixels))。

在同步快门模式下,帧频Frame period="Tint"+Tread out="Tint"+(Nr.Lines×(RBT+Pixel Period×Nr.Pixels))。其中,Tint为积分(曝光)时间;Nr.Lines为每帧读出的行数;Nr.Pixels为每行读出的像素数;RBT为行空白时间(典型值为3.5 ms);Pixel Period为1/40 MHz="25" ns。

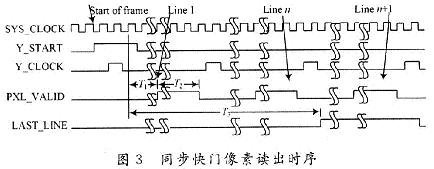

卷帘快门中有两个y方向的移位寄存器,一个指向正在被读出的行,另一个指向正在被复位的行,两个指针由同一时钟y_clock(行时钟)驱动,它们之间的差值代表了光积分时间。在卷帘快门模式下,像素的读出和复位同时进行,每行像素的复位和读出是顺序进行的(见图3)。像素的积分时间可以通过寄存器INT_TIME来修改。在这种模式下,像素在不同的时刻感光,因而在采集动态图像时会产生模糊。

在同步快门模式下,所有像素的光积分在同一时刻进行的。所有像素同时被复位,在经过光积分后,像素的值被存储在每个像素的存储节点上,然后逐行依次读出。像素的光积分和读出是串行的,在像素读出时,积分被禁止,因而可以避免卷帘快门所产生的动态图像模糊的问题。此外,同步快门支持多斜率积分,可获得比卷帘快门更高的动态范围。

综上分析,在使用这款成像器芯片时,对快门方式要根据应用的场合进行选择,在对快速运动的物体进行捕获或要求有高的动态范围时应选择同步快门;而在对图像的帧速率要求较高或要对图像进行连续采集时应选择卷帘快门。

2 基于FPGA的CMOS控制时序的设计

2.1 现场可编程门阵列FPGA

随着集成电路的发展,大规模可编程逻辑器件广泛用于电路设计领域,它具有功耗低,可靠性高的特点,同时大大减小了电路板的尺寸。FPGA的内部结构决定了FPGA在时序设计方面的优越性。该设计选用Xilinx公司的Spartan3系列FPGA芯片XC3$50作为硬件设计平台。Spar-tan3基于VirtexⅡFPGA架构,采用90 nm技术,8层金属工艺,内嵌硬核乘法器和数字时钟管理模块。从结构上看,它将逻辑、存储器、数字运算、数字处理器、I/O以及系统管理资源完美地结合在一起,使之具有更高层次、更广泛的应用。

相关推荐

在线研讨会

焦点