等精度频率计的实现

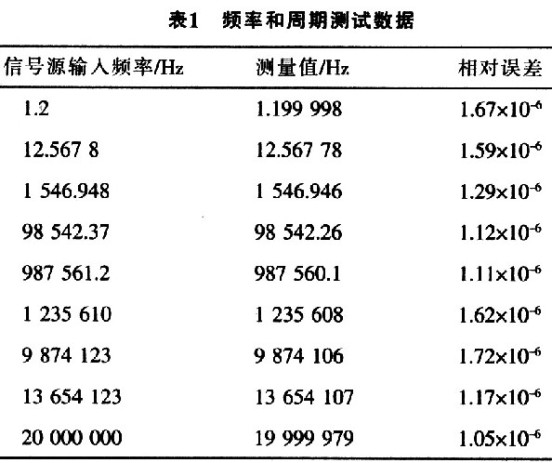

采用高精度信号源输出不同频率的正弦波信号,经过信号调理电路,整形得到的方波信号提供给FPGA进行计数测量,将测量结果与高精度信号源输出的频率相比较,计算其误差,如表1所示。

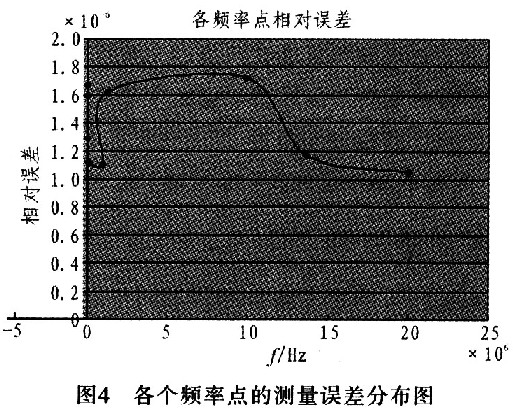

表l给出了各种频率的测量结果和误差。结果显示,本设计在1Hz~20MHz全范围内的测量误差小于2×10-6。从图4可以看出测量结果的误差分布在同一个数量级附近,达到了等精度测量的目的。在实际测试中发现,如果提高系统晶振的频率或者提高晶振的精度级别,频率测量的误差还会进一步降低。

4 结束语

详细介绍了等精度测量的原理,并给出等精度测量的思想在FPGA上实现的方法。测试结果表明该等精度测量方案误差非常小,在测量范围内误差恒定。该设计方案对测量频率实现设计具有一定的借鉴。

相关推荐

在线研讨会

焦点