基于FPGA的高速通信系统研究

2.3 电路PCB设计

在PCB设计过程中,要注意电路板的布局。模拟电路和数字电路需要分开,使用单点接地的方式相连。将边沿速率变化快的VTTL/LVCMOS信号与LVDS信号布在不同信号层上,并用电源和底层隔开,减小耦合到LVDS线路上的串扰。LVDS走线要遵循以下规则:

(1)差分对两根信号从芯片扇出后就尽量靠近(紧耦合),这样有助于消除反射,确保耦合的噪声是共模形式。

(2)对内信号的布线长度要保持一致,以减小信号延时,长度匹配控制在10 mil以内。

(3)对内信号保持固定的线间距,避免因为线间距变化导致差分阻抗不连续。

(4)差分对间尽量远离,减少线间串扰,必要时在差分对间放置隔离用的接地过孔。

(5)尽量减少差分信号线上过孔的个数,避免走90°拐角,使用圆弧或者45°折线代替。

(6)LVDS信号不能跨平面分割,否则会因为缺少参考平面而导致阻抗不连续,要给LVDS信号设置完整的参考平面。

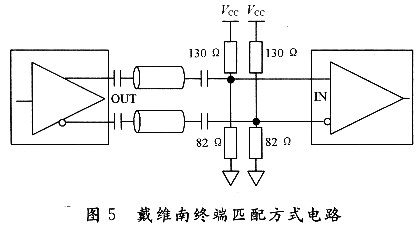

(7)匹配电阻尽可能靠近接收端。

3 系统的逻辑设计

3.1 时钟部分设计

时钟信号由电路板上40 MHz晶振提供。通过数字时钟管理单元DCM钟倍频得到120 MHz的系统的工作时钟。使用DCM模块时,注意DCM的输入和输出需要通过BUFG单元与全局时钟资源相连。全局时钟资源使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,使全局时钟到达芯片内部所有逻辑单元的时延和抖动都为最小。DCM在时钟锁定后使能LOCK信号,表示时钟倍频工作完成,使用这个信号作为FPGA内部其他逻辑的复位。

3.2 异步时钟域变换

系统输入信号工作在不同的异步时钟域,需要在FPGA内部将信号变换到同一个时钟域。

串口信号速度低,可以使用系统时钟高速采集的方式。根据奈奎斯特抽样定律,抽样频率大于2倍信号最高频率,就可以从抽样信号中无失真地恢复原信号。本系统使用高于5倍串口波特率的时钟去采集串口数据。经过误码仪的大量测试,串口数据能够被正确接收和恢复。

视频信号是并行信号,采用高速采集的方法会增加数据量,不适合本系统。本系统采用双口FIFO完成异步时钟域转换。S

3.3 数据组帧及编码

同步传输需要将原始数据组成数据帧再进行发送,即在数据间添加起始位、停止位和校验位。数据帧的起始位过长会影响传输效率,过短会增加接收端识别的难度。本系统选用80 b为一帧,起始位为8 b,停止位为2 b,奇校验位为1 b。接收端逻辑通过对多个数据帧分析后,定位数据帧的起始位。由于每帧数据长度固定,所以找到某一帧的起始位后可以周期性的计算出接下来各帧的起始位置,不再需要反复做识别工作。

数据组帧后信号的平均位速率可能低于CLC012的最低工作频率,不能直接用于传输,还需要对其进行8B/10B编码。8B/10B技术是将8个数据位经过某种映射的机制转化为10个数据位的字码,可使发送的“O”、“

4 结语

介绍了一种基于FPGA的高速通信系统,通过电缆驱动器和接收均衡器,拓展了LVDS信号的传输距离。经过测试,使用同轴电缆的传输距离达到