航天地面测试中1553B-PCI接口转换技术实现

1 引言

1553B 总线是MIL-STD-1553B 总线的简称,其全称为飞机内部时分制指令/响应式多路 传输数据总线,是一种满足实时性、数据完整性和系统可靠性的通用机载串行多路总线标 准,该总线标准首先在航空工业中得到广泛应用。随着卫星技术的发展,1553B 总线在国 内航天领域的应用也日益广泛,作为与之配套的地面检测设备也需要具有1553B 总线接口 的通信板卡。

2 方案设计

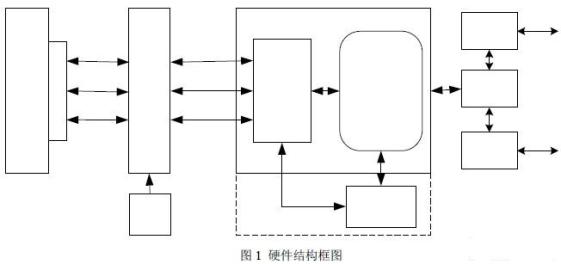

本板卡是基于PCI 总线的1553B 总线接口卡,要实现的功能是利用PCI 总线作为媒介, 实现计算机控制1553B 总线BC 端和RT 端进行数据传输的功能,最终在卫星地面测试过程中 实现由计算机对远程终端的设备进行测试和控制。板卡硬件结构如图1 所示,主要由PCI 协议接口芯片、1553B 总线控制器、收发器和变压器等组成。

3 PCI-1553B 接口卡功能实现

3.1 1553B 协议

1553B 总线系统中包含三种不同类型的终端:总线控制器(BC)、总线监视器(MT)和 远程终端(RT)。由于1553B 数据总线采用的是主从控制方式的总线控制,主节点即总线控 制器(BC)负责控制整个网络,控制数据流从BC 流向RT、RT 流向BC 以及RT 流向RT。数 据流的基本形式是消息,协议规定一个消息传输的完整过程由指令字、数据字(或指令字和 状态字)组成。每一种字长为20 位,有效消息位是16 位,每种字的前三位为同步头,最后 一位是奇偶校验位。在本系统中,主要数据传输方式是BC→RT 和RT→BC 两种。 BC 端向RT 端的数据传输过程是首先由BC 发出一个接收指令字及规定数目的数据字到 RT,后者在核实消息后发回一个状态字给BC,指令字和数据字应以没有字间间隔的连续形 式发出。

RT 端向BC 端的数据传输过程是首先由BC 向RT 发出一个发送指令字,该RT 在核实指 令字后,发回一个状态字给BC,继之以规定数目的数据字,状态字和数据字应以没有字间 间隔的连续形式发出。

3.2 1553B 总线协议控制器的实现

1553B 总线协议控制器是本板卡构成的关键。市场上实现1553B 总线协议的芯片很多, 目前应用比较广泛的是美国数据设备公司(DDC)的BU-61580,它虽然能够完整的实现 1553B 总线协议,但缺点是设置比较复杂、体积比较大、功耗比较高。本设计采用Condor Engineering 公司的FlightCORE-1553 IP 核作为总线协议控制器,它完全满足1553B 总线协 议,为主处理器和1553B 总线提供了完整、灵活的接口,能够实现总线控制器(BC)、远程 终端(RT)和总线监视器(BM)三种模式,并且适应ALTEA 和XILINX 大部分型号的FPGA, 与BU-61580 等协议芯片相比,具有使用灵活、功耗低、节省印制板面积等特点。

该总线控制器内部有 1K×16bits 的存储空间,在存储空间的低地址区是硬件寄存器、 固件保留区和文件寄存器,通过对这些寄存器的设置,可以方便地将控制器配置为BC、RT 或者BM。

下面对常用的寄存器进行说明: 1. 配置寄存器:用来选择工作模式,即 BC、RT 或BM;

2. 控制寄存器:用来启动相应的工作模式;

3. 中断使能寄存器:设置产生中断的条件;

4. 中断状态寄存器:当中断产生时,固件将该寄存器相应位设置为有效,主处理器通 过读该寄存器判断是否有中断发生;

5. 自检寄存器:该寄存器具有只读属性,表明工作状态。 实际应用中,该控制器需要4K 字的存储空间才能正常工作,所以需要扩充存储空间, 考虑到控制器接收处理总线数据后计算机能及时获取而又不影响其正常工作,采用双口RAM 比较合适,其中控制器前1K 字的存储空间和双口RAM 的地址空间是重叠的。

3.3 PCI 功能的实现

PCI 协议接口芯片采用PLX9054,通过XILINX 的FPGA 实现PLX9054 与1553 总线协议的 通信。当计算机启动时,9054 需要串行EEPROM 为其提供一些必要的配置信息以实现对PCI 配置寄存器和本地寄存器的设置,这些信息除了局部空间的范围和基地址外,还包括设备信 息和中断资源等,这些需要我们事先烧写到EEPROM 中,本文EEPROM 采用93LC56B。

实际应用中,需要根据存储空间大小配置相应的9054 的地址空间,1553B 总线控制器 本身含有1K 字的寄存器空间,为了扩大存储器空间,在FPGA 内例化了8K×16bits 的双口 RAM。在9054 的本地端,将地址总线设为32 位,每一次32 位的读写操作仅对其低16 位进 行,高16 位未用,因此实际需要配置2 倍于双口RAM 大小的空间,即32KByte,故EEPROM 中的局部地址空间0 范围寄存器设为FFFF8000,局部地址空间0 描述寄存器设为4B430043。

3.4 PCI 总线和1553B 总线的桥接

在PCI 总线一边,9054 的PCI 总线端需要和主机上的PCI 插槽进行连接。由于9054 是 专用的PCI 协议芯片,所以它的PCI 端可以直接通过插卡上的引线和PCI 插槽连接。

9054 的本地端和1553B 总线控制器HOST 端通过FPGA 实现逻辑转换。9054 支持三种传 输模式,即主模式、从模式和DMA 模式,DMA 模式适合突发的大量数据的传输,由于1553B 总线的数据速率为1Mbps,数据量很小,因此采用从模式中的单周期读写模式,相对于主模 式而言电路设计和时序控制也相对简单。

根据9054 从模式下单周期读写时序、1553B 总线控制器HOST 端时序和双口RAM 时序采 用如图2 所示的状态机实现PCI 总线对1553B 总线控制器和双口RAM 空间的读写操作。

图2 状态转换图

当9054 的局部总线复位信号有效后,状态机进入S0 状态,当启动本地总线的单周期写 操作时,在检测到地址选通信号有效,且写信号有效后,状态机进入S1 状态,将本地地址 总线赋给1553B 总线控制器的地址总线,状态机进入S2 状态,将本地数据总线赋给1553B 总线控制器的数据总线,直到数据写入后,状态机重新回到S0 状态;当启动本地总线单周 期读操作时,在地址选通信号有效且读信号有效后判断本地地址总线,当本地地址大于等于 1024 时,访问双口RAM 的B 端口,当本地地址小于1024 时,访问1553B 总线控制器内的寄 存器,这样做的好处是防止对双口RAM 操作时出现读写冲突的问题。