一种数字示波器的微处理器硬件设计

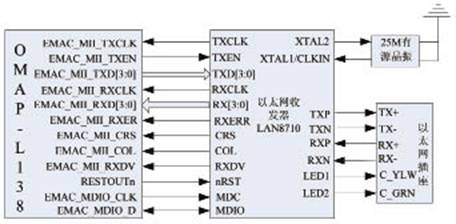

以太网接口连接示意图如图6所示:

图6 以太网接口连接示意图

本设计采用外接

结论

本设计有以下优点:数据处理与系统控制同步执行;微处理器内部存储资源丰富,且采用二级缓存结构,系统响应速度快;外设资源丰富,提供了如USB接口、RS232接口和以太网接口等与PC机互联的接口,方便示波器上采集到的波形数据在PC机上实时处理和在线调试;外部存储器资源丰富,采用1Gbit 容量的DDR2 SDRAM作后级波形数据缓存区和显示数据缓存区,能够存储更多波形数据,观察到更多波形细节。由此可见,采用该示波器系统可大幅提高数字示波器的数据处理能力和波形捕获率,整机的响应速度也将上一个台阶。

相关推荐

在线研讨会

焦点