板级电路内建自测试建模技术研究

4. 结论

本文通过建立高速数据采集器的多信号流模型,对数据采集器进行了可测性分析与可测性设计,通过可测性设计其故障检测率和故障隔离率均达到100% ,在此基础上可以通过DSP 完成整个电路的自测试。本文的研究成果为提高电路的自测试能力奠定基础,可适应现场快速故障诊断和故障定位的需要。本文作者创新点:提出了一种板级电路内建自测试建模技术,针对原有电子系统增加内建自测试的可测性技术,并采用多信号流作为评估方法,通过实际系统验证了所提出方法的可行性和实际价值。

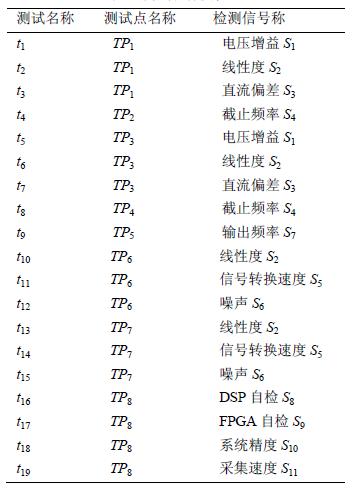

表4 测试名称及位置

表5 可测性改善对比表

参考文献

[1] GJB2547-95 .装备测试性大纲[S].北京:国家科学技术工业委员会,1995

[2] 田仲,石君友.系统测试性设计分析与验证[M].北京:北京航空航天大学出版社,2003

[3] 康中尉.可测试性设计研究[J]《.微计算机信息》,2008,1-1:157-159

[4] SOMNATH Deb, KRISHHA R PatTIpati, VIJAY Raghavan, et al.Multi-signal flow graphs: a novel approach for system testability analysis and fault diagnosis.1994 IEEE Autotestcon Proceedings, 1994, 361-373

[5] Deb, S., Ghoshal, S., Malepati, V.N. and Kleinman, D.L., 2000, Tele-diagnosis: Remote monitoring of large-scale systems, Proceedings of the IEEE Aerospace Conference, Big Sky,MT

[6] 杨智勇,许爱强,牛双诚.基于多信号模型的系统测试性建模与分析[J].工程设计学报,2007,14(5):364-368,394

[7] Jianhui Luo, Haiying Tu, Krishna Pattipati, Liu Qiao and Shunsuke Chigusa, “Graphical models for diagnostic knowledge representation and inference,” IEEE Instrument and Measurement Magazine, Vol. 9, No. 4, pp. 45 – 52, Aug., 2006

[8]Jianhui Luo, Kihoon Choi, Krishna R. Pattipati, Liu Qiao and Shunsuke Chigusa, “Distributed fault diagnosis for networked, embedded automotive and aerospace systems,” Proc. Of IEEE International Conference on Systems, Man, and Cybernetics, Taipei, Taiwan, Oct., 2006

[9] F. Tu, K. R. Pattipati, S. Deb, and V. N. Malepati, “Computationally efficient algorithms for multiple fault diagnosis in large graph-based systems,” IEEE Transactions on Systems, Man and Cybernetics–Part A, vol. 33, no. 12, pp. 73–85, 2003

[10]M. Shakeri, “Advances in system faultmodeling and diagnosis,” Ph.D. dissertation, Univ. of Connecticut, Storrs, 1996

[11]G. Simon, G. Biswas, S. Abdelwahed, N. Mahadevan, T. Szemethy, G. Peceli, and T. Kovashazy, “Model-based fault-adaptive control of complex dynamic systems,” in Proc. Instrumentation Measurement TechnologyConf., Vail, CO, May, 20–22 2003