嵌入式DSP访问片外SDRAM的低功耗设计研究

3.2 写后缓冲区的设计

数据在存储器中的存放位置可能不像程序空间那么连续,而且数据空间有读写,对数据空间读写SDRAM进行优化的基本思想是,归并对SDRAM同一行的读写操作。具体来说,包括归并对同一行的多个读操作、归并对同一行的多个写操作,归并对同一行的多个读写操作3种情况,文献提出了这种设计方法,其基本思想是:系统从预取缓冲区(FB,Fetch Buffer)中取数据;写数据时,先写到写归并缓冲区(WCB,Write Combine Buffer);对在FB或WCB中的同一行的读写请求进行归并。但此设计方法是针对有一级Cache的通用微处理器系统,过于复杂,实现代价过高,不适合于本文研究的没有一级数据Cache的DSP,因此这里采用写后缓冲区(Write Post Buffer)的方法,具体设计方法如下:

1)在EMIF中设立一个写后缓冲区,所有对SDRAM的读写请求均送到写后缓冲区,写后缓冲区立即给CPU响应,CPU可以不用等待写操作的结束而继续执行程序。

2)每当写后缓冲区接受到一个新的写请求后,首先判断写后寄存器中是否存在和该写操作在SDRAM同一行的写操作,若有,将这两个写操作归并后同时向SDRAM进行写。

3)当CPU读数据时,首先检查写后缓冲区,若存在要读的数据,直接从写后缓冲区读数据;若不存在,则从写后缓冲区中挑选和当前读操作在同一行的写操作归并后,对SDRAM进行读、写操作。

设计写后缓冲区不仅可以提高程序的执行效率,还可以节省功耗。综合考虑系统的性能与功耗要求,这里DSP写后缓冲区设计为8 KB,采用和I-Cache类似的结构。

3.3 动态监测总线利用率

SDRAM在所有的行都打开,等待读写操作时的功耗是所有行都关闭时的2倍多,因此SDRAM为了低功耗的需要,设计时都加入了休眠模式。当对同一行有大量的读写时,又需要采用开放的页策略,维持这些行打开。考虑到SDRAM的这些特点,单独采用开放的页策略或封闭的页策略是不合适的,需要结合运用。动态监测EMIF总线的利用率,块读、块写和读写归并时采用开放的页策略,当总线利用率较低时,采用封闭的页策略,当总线利用率很低时,将SDRAM进入休眠模式,需要时再澈活。

以MT48LC

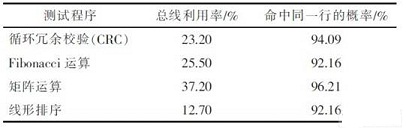

文献统计了通用处理器中不同程序的总线的利用率,如表1所示。可见,对于不同的程序,总线利用率差别较大。根据当前总线的利用率来决定采用何种策略访问SDRAM是比较合适的。

表1

4 优化后的EMIF的性能分析

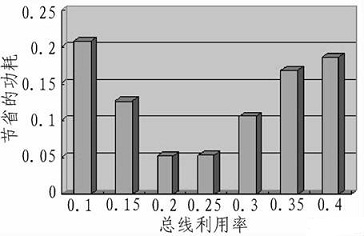

对采用的总线监测的读写归并方案进行计算,假设前后命中同一行的概率是90%,根据Micron数据手册计算,归并两个写操作功耗减少24%,对不同的总线利用率的计算结果如图3所示。

图3 基于总线监测的读写归并方案功耗计算

5 结束语

在基于DSP的嵌入式应用系统中,存储系统的功耗占据系统功耗的大部分。当外部存储器采用SDRAM时,降低SDRAM的换行访问可以节约大量的功耗。本文设计的基于总线监测的读写归并方案,不仅降低了外部存储系统的功耗,而且可以在一定程度上提高存储系统的性能。加入的I-Cache可以使程序总线更快地读指令,加入的写后缓冲区(WPB)可以使CPU不用等待缓慢的外部写操作的结束而直接继续执行指令。