第四代无线基础架构的离散式 SerDes 解决方案

图

图

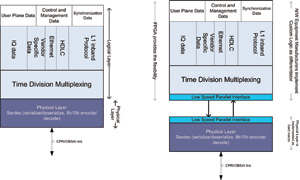

图3b CPRI通信协议层堆栈(外部SerDes划分)

由于网络设备制造商改采

以下是选择离散式SerDes-FPGA及整合型SerDes-FPGA时必须考虑的几项关键因素:

● 离散式SerDes加上FPGA的成本VS已整合SerDes的FPGA成本

● 离散式SerDes的效能VS整合于FPGA的SerDes效能

● 对于特定FPGA平台的熟悉程度

● 改用整合型SerDes-FPGA所节省的空间

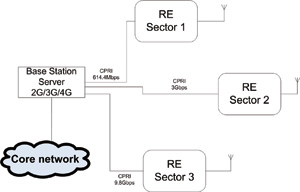

图4显示

图4 连接到3个RE的

状况A:假设网络设备制造商使用FPGA与离散式SerDes,而且已经在该特定FPGA平台的学习周期中投入时间与资源。若要在此状况下支持9.8Gbps:

● 制造商将SerDes升级,并持续使用同一个熟悉的FPGA平台。优点:达到规模效益,因为图4显示的3个RE区块都能具备类似的FPGA,同时以不同的SDR进行运作。如此一来,制造商便不需要变更FPGA平台而经历学习周期。

状况B:网络设备制造商使用已整合SerDes功能的经济型低阶FPGA。若要在此状况下支持9.8Gbps,制造商有3种选择:

● 改用不同制造商的9.8Gbps高阶FPGA(已整合SerDes)。缺点:成本增加,而且制造商必须经历新FPGA平台的学习周期。

● 改用相同制造商的低价9.8Gbps FPGA(已整合SerDes)。缺点:效能疑虑。

● 向同一个厂商购买不含SerDes的FPGA,并将系统切割为FPGA以及离散式SerDes。优点:制造商改用不含SerDes的FPGA可以节省成本,同时保留熟悉的FPGA平台。此外,使用相同的FPGA可切割出采用离散式SerDes的3个RE区块,进而达到规模效益,就如图4所示。缺点:离散式SerDes加FPGA的解决方案可能需要更多的PCB空间。

状况C:网络设备制造商使用已整合SerDes的高阶FPGA。若要在此状况下支持9.8Gbps,制造商有3种选择:

● 改用相同制造商的9.8Gbps FPGA(已整合SerDes)。缺点:制造商可能必须为具备9.8Gbps SerDes功能的FPGA付出相当高的成本。

● 改用不同制造商的9.8Gbps低阶FPGA(已整合SerDes)。缺点:学习周期、效能疑虑、缺乏降低成本的规模效益。

● 向同一个厂商购买不含SerDes的FPGA,并将系统切割为FPGA及离散式SerDes。优点:与状况B类似。

在9.8Gbps或12Gbps等高SDR的情况下,要满足离散式SerDes设计中对于稳定频率数据复原、抖动容差、信号调节及信号完整性的需求已经相当不容易,更不用说在整合型SerDes-FPGA设计中,数字逻辑项目区块(芯片的大部份)内敏感模拟电路的噪声隔离会造成设计上更大的挑战。有时候,为达到所需的效能,已整合SerDes的FPGA需要高成本的电源供应滤波,并选择使用电压控制的晶体振荡器或成本较低的晶体振荡器。这些需求会增加实施的成本。概括来说,将SerDes整合于FPGA会造成相关的成本,而且当整合难度因为SDR升高而增加时,这些成本也会增加。这正是为何当数据速率在3Gbps或更低的状况下,FPGA加离散式SerDes的解决方案比整合型解决方案更符合成本效益的一个主要原因。

结论

当网络设备制造商建置