FPGA设计及多片FPGA进行ASIC设计验证的探讨研究

摘 要:在ASIC设计中, 校验是一个非常重要的部分,一般先要进行FPGA 验证。FPGA 验征有一整套严格的流程;随着ASIC设计越来越庞大、越来越复杂, 单片FPGA 已不能满足设计验证要求, 多片FPGA 验证应运而生。多片FPGA验证还处于起步阶段, 其验证方法和工具有很大的研究和发展空间。关键词:现场可编辑门阵列;专用集成电路;验证

一、FPGA 设计流程

1. 1 FPGA 简介

现场可编程门门阵列FPGA (Field Programmable Gate Array) 是20 世纪80 年代中期出现的高密度可编程逻辑器件。FPGA 具有掩膜可编程门阵列的通用结构, 它由逻辑功能块排成阵列, 并由可编程的互连资源连接这些逻辑功能块来实现不同的设计。FPGA 一般由3 种可编程电路(可编程逻辑块CLB、输入/输出模块IOB 和互连资源IR) 和一个用于存放编程数据的静态存储器SRAM 组成。 可看成是一种半定制的专用集成电路(ASIC) , 它克服了原有PLD 电路数有限的缺点, 是一种灵活有效的数字集成电路的设计和验证工具。FPGA 开发周期短, 费用低, 采用FPGA 设计A S IC 电路, 用户不需投片生产就能得到合用的芯片; FPGA 可以在实现算法的手段上更具灵活性, 能加快算法实现速度, 提高实时性。

1.2 设计流程图

二、多片FPGA 验证ASIC 的探讨研究

2.1 多片FPGA 验证

随着先进的半导体工艺技术不断提高, 深亚微米(DSM )工艺技术使得在芯片上的构造更多的门电路成为可能, 并能够实现包含各种IP以及存储器和软件的系统级芯片(SoC) ,这带来的是ASIC 设计规模和设计复杂度的飞速增长。

ASIC设计规模的增大, 在带来实现高性能芯片系统可能性的同时, 也带来了前所未有的芯片验证问题。在百万门ASIC 的设计之前, 我们通常是把设计放在一块FPGA 中进行功能验证; 但随着百万门ASIC 的出现, 最大的FPGA 的容量也不足以装下百万门甚至几百万门的设计, 这就意味着设计者必须把他们的设计分割到几块FPGA 中。在IC 设计中, 验证通常至少占到工作量的50% , 对于超大型设计, 验证已占到了70%。若验证方法和工具的滞后, 将严重阻碍IC 设计的发展。因此, 可以说校验(Verificat ion) 问题是当今IC 设计的最大瓶颈, 而且随着越来越多的需要处理大量实时数据的应用, 验证技术就要求能够在接近实时频率的条件下进行验证。

如何进行方便灵活的测试和验证成为人们关注的焦点之一。

对于单块FPGA 验证是经济高效的, 但是也会遇到由于设计不当造成的时序问题。其一是毛刺信号。无法预见毛刺信号可通过设计来传播并产生不需要的时钟脉冲。当毛刺号影响后续电路时, 就成为一个较大的问题。其二是时钟问题。使用逻辑门控制时钟信号, 会在时钟和数据之间产生较多的扭曲。其三是复位问题。同时钟问题一样, 如果使用组合逻辑或者不详细考虑时序, 复位信号也能产生一系列问题。还有执行问题, 实验方法问题等等。这些问题可以通过好的设计技术减至最少, 并且可以使得门阵列的转换变得更为平稳。

对于多片FPGA 验证来说, 就有许多问题有待解决。首先问题是如何把整个设计分割到多片FPGA 中, 如何分配每个FPGA 的I/O。ASIC 设计者通常使用定制或是可重构的验证环境来做系统验证; 常会花费很长的周期, 因为在验证的过程中综合和分割是分不开的。综合的时候不会考虑到设计如何分割到多片FPGA , 因此, 与希望的速度有很大差距。分割的方法也不能反馈, 不会对利用率和系统性能带来影响。因此, 设计者会在分割和综合之间反复多次。若要对源代码进行修改, 那么这一过程还要反复多次。所以一个很好的解决问题的方法是把FPGA 分割和综合结合起来, 并且在RTL级完成分割。要在RTL 级完成分割就要一定的分割和综合算法。如何分割可以减少系统开支, 怎样来减弱或消除时间延迟, 都是必须考虑的问题。

现在有多个公司生产FPGA , 如Xilinx,Altera 公司等。每种FPGA 虽然原理、基本结构是相类似的, 但还是有许多不同之处, 要对多片FPGA 进行验证必须考虑到各种FPGA 的特殊结构。目前, 已有公司开发了专门针对FPGA 多芯片验证的仿真工具, 比如Synplicity 的Certufy, Certufy 是建立在Synplicity 综合技术上的, 核心算法包括了适合各种FPGA 特殊结构的综合算法, 它的时序驱动的综合算使设计可以达到尽可能高的系统速度。这种综合算法的内核被扩展到了运用独特的分割驱动综合算法的Certify 中。有了这种方法, 综合过程就基于一个确定的分割。在多片FPGA 之间的时间预算自动被包含在分割驱动的综合算法中。这个方法是Certify 解决方案的核心, 提高了验证性能。

但作为一个新兴的技术, FPGA 多芯片验证还不能指望一家公司开发的一个工具解决所有问题。由于ASIC 设计的结构方案不一样, 所以验证中出现的问题也是各式各样的; 所以, 大型ASIC设计的FPGA 多芯片验证, 从工具到方法学上, 有很大的发展空间。

对于ASIC 设计者设计的芯片可粗略的分成几个大类,针对每个大类的ASIC 设计专用的多芯片FPGA 验证方法。当有针对性的对某一类ASIC设计是, 就可以把某些问题细节化具体化, 能更好地提供解决方案。在多征FPGA 验证方法中要解决三大类问题:

(1) 单个FPGA 验证中存在的问题。

(2) 分割多块FPGA 所带来的问题。

(3) 出现的未曾估计到的问题。

对于第一类问题, 已经可以通过改进设计来很好的解决; 对于第二类问题, 正是目前最需研究的课题, 这包括新的分割方法、综合算法的提出, 系统资源的分配, 以及针对新的方法的测试等; 对于第三类问题就需要灵活的解决。

2. 2 多片FPGA 间互连的拓扑结构

多片FPGA 验证系统除了要考虑内部分割综合这一大问题之外, 还要考虑整个系统的物理连接结构。设计多片FPGA 验证系统的一个重要的步骤是决定多片FPGA 间的互连拓扑结构。拓扑结构结系统总体性能有很大的影响。多片FPGA 系统互连结构主要有固定连线的网络型(mesh, 见图1, 2) 和可编程的交叉开关型(crossbar, 见图3) 这两种互连结构有一定的缺陷; 如何克服缺陷, 获得最佳性能是多片FPGA 验证系统中又一大研究课题。

图1 网络型(mesh) 结构 图2 4 向mesh 与8 向mesh 对比

2.3 多片FPGA 的测试

当一种新的多片FPGA 验证方法提出以后, 就必须对其进行测试。测试可分为两大步聚进行。第一, 在FPGA 不混合任何附加的硬件; 第二, 在FPGA 外围连接了许多硬件电路进行综合测试; 最基础的测试是第一步测试。

图3 crossbar 互连结构

对于第一步的多片FPGA 测试一般可任意选一块FPGA作为主测试芯片(MASTER FPGA ) , 剩余的FPGA 作为伺候服务芯片(SLAVE FPGA )。主测试FPGA 产生测试模式来测试伺候服务FPGA , 分析伺候服务FPGA 的输出应答并全面的控制整个内部测试机制; 主测试FPGA 有测试模式产生器(TPG)、输出应答分析器(ORA ) 和其它产生控制信号的逻辑映射在它上面。在任意给定的时间, 每片FPGA 内部的某组CLB 被同时测试, 直到所有的FPGA 中的所有CLB 都被测试完成。而同一时间测试的伺候服务FPGA 数目和每块伺候服务FPGA 可同时测试的CLB 数目是由主测试FPGA 的可利用的逻辑数目和IOB p in 脚的数目决定。图4以有8 块FPGA构成的多片FPGA验证系统为例。

对于主测试FPGA , 有两部分是非常重要的: 测试模式产生器(TPG) 和输出应答分析器(OPA )。这两部分分别可以有多种设计, 不同的设计对应不同的测试方法。如图1, 此种TPG 由一个存储模式的ROM , 一个4 位的线性反馈转换寄存器和一个3 位的控制输入计数器组成。输出应答分析器一般的工作原理是先输出所有伺候服务FPGA 的第一个CLB, 并相互之间进行比较。理论上比较的结果应该是相同的; 如果出现不同, 就意味着它们中一个出现了错误, 继续比较第二个CLB, 来确定到底是哪个FPGA 出了差错。此外, 控制部分也很重要, 它掌握着测试过程的顺序。

图4 8 块FPGA 测试方案的结构图

第一步也是最关键的,测试完成后, 可连入其它硬件电路设备进行综合测试。通过了最后的综合测试就说明这种新的多片FPGA 的验证方法是可行的。

当然, 针对每一类的ASIC 设计的多片FPGA 验证方法通常可以较好的解决一类验证问题; 但也有不足之处: 通用性稍差。鉴于此, 也可以设计比较通用的多片FPGA 验证方法;这样设计、测试阶段的工作量就大大增加, 但是一旦设计成功将会有更大的应用空间。

三、结论

对于多片FPGA 验证ASIC设计领域有很大的研究发展空间。多片FPGA系统验证方法将会不断的出现, 专用验证工具也会不断的涌现。

相关推荐

微捷码FineSim SPICE被作为标准验证工具

2009-05-06

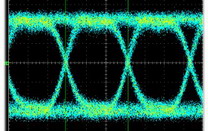

泰克仪器用于3Gb/s监视器设计验证和测试

2009-04-24

在线研讨会

焦点