机载电子盘设计

摘要:本文介绍了机载电子盘的硬件设计、调试和软件测试方法。该系统满足了机载航空图数据处理量大、吞吐率高、环境恶劣的环境要求,在嵌入式电子盘设计中具有典型性和实用性。内容充实,信息量大,工程实践性强。

关键词:电子盘;与非阵列;IDE接口;写保护

中美撞机,勇士入海,“浪花与泪花齐飞,海水共长天黯色”。从此,制造新一代功能强大的、能及时搜索、导航和定位的营救机,成为国人注目的大事。这不仅需要功能强大的搜索雷达,同时需要功能强大的处理定位计算机。采用电子航空图和多普勒雷达、GPS及惯导组成综合导航系统就是增强营救机功能的重要举措。在航空图上能够对导航参数形象直观、及时准确的换算定位,将飞行员从繁多的、令人头疼的导航仪表和枯燥的需大量记忆的数据中彻底解放出来。但是通常的机载计算机只配有小容量存储器,采用诸如VxWorks等字符操作系统,无法显示和处理全国范围的小比例尺的航空地图。显示和处理大数据量的共同瓶颈在于没有适合机载的硬盘,无法采用图形操作系统和存贮大容量数据。本文介绍我们在解决这一问题的一些做法,与大家切磋。

一 IDE接口概述

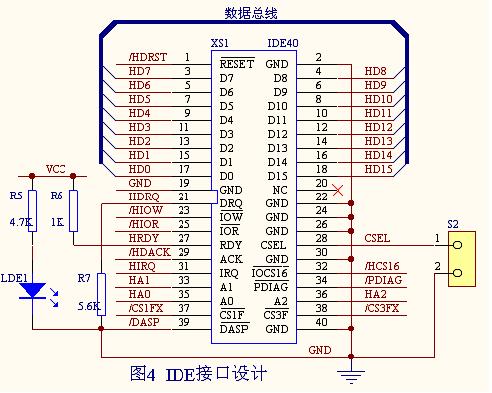

目前硬盘接口以IDE(Intelligent Device Electronics)为主,又称ATA(AT-Attachment)接口。其主要特点是把原来ST-506接口的控制器部分移到驱动器中去,使得主机的IDE适配电路并不包括硬盘控制器,扩大了适应性,亦可连接CD-ROM等设备。IDE接口一般采用40线转插,信号名称和位置可参考图4的电路,它是16-Bit总线。表1是接口内部寄存器分配。

表1 IDE接口内部寄存器映象

|

/CS3FX |

/CS1FX |

A2 A1 A0 |

寄 存 器 | |

|

读操作 (/IOR=0, /IOW=1) |

写操作 (/IOR=1, /IOW=0) | |||

|

1 |

0 |

0 0 0 |

数据 (读) |

数据 (写) |

|

1 |

0 |

0 0 1 |

错误 (Error) |

特征 (Feature) |

|

1 |

0 |

0 1 0 |

扇区数 (Sector Count) |

扇区数 (Sector Count) |

|

1 |

0 |

0 1 1 |

扇区号 (Sector Number) (LBA7-0) |

扇区号 (Sector Number) (LBA7-0) |

|

1 |

0 |

1 0 0 |

柱面低(Cylinder Low) (LBA15-8) |

柱面低(Cylinder Low) (LBA15-8) |

|

1 |

0 |

1 0 1 |

柱面高(Cylinder Hight) (LBA23-16) |

柱面高(Cylinder Hight) (LBA23-16) |

|

1 |

0 |

1 1 0 |

驱动器/磁头 (Drive/Head) |

驱动器/磁头 (Drive/Head) |

|

1 |

0 |

1 1 1 |

状态 (Status) |

命令 (Command) |

|

0 |

1 |

1 1 0 |

后备状态 (Alternate Status) |

设备控制 (Device Control) |

|

0 |

1 |

1 1 1 |

驱动地址 (Drive Address) |

保留 (Reserved) |

在PC机中IDE接口作为I/O外设处理,一般有2个IDE接口。主要片选信号线/CS1FX、/CS3FX对应的译码地址如表2所示,表中同时给出了IRQ资源占用。/CS1FX有效(低电平)时选择命令寄存器,/CS3FX有效时选择控制寄存器。IDE接口对硬盘有两种操作方式。一是物理寻址(CHS-Cylinder/Head/Sector)模式,即主机应该具体给出要读写的柱面/磁头/扇区,另一是逻辑块寻址(LBA-Logical Block Address)模式。在LBA模式下,将所有扇区按照柱面优先的原则编号,组成线性扇区地址。由IDE控制器把逻辑扇区号译码为对应的CHS后再操作。一个逻辑块容量等同一个物理扇区,亦即512字节。在机械式磁盘结构时,LBA模式可使连续扇区操作节省磁头移动定位时间。软件采用LBA模式操作,可以简化管理算法。

表2 IDE接口I/O地址范围及资源分配

|

|

/CS1FX |

/CS3FX |

中断请求 |

DMA请求 |

|

第一IDE接口 |

1F0H—1F7H |

3F0H—3F7H |

IRQ14 |

DRQ3 |

|

第二IDE接口 |

170H—177H |

370H—377H |

IRQ15 |

DRQ4 |

二 IDE控制器SST55LD017

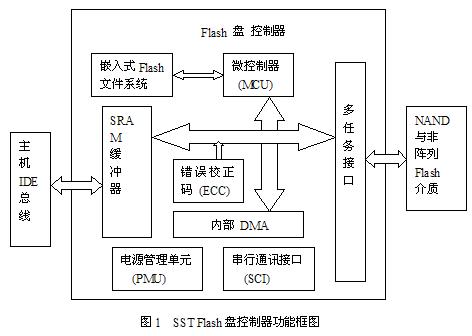

实现IDE接口的办法有多种,世界著名的电子盘生产商BiTMCRO生产的电子盘内嵌入了PowerPC 403来组成控制器,这种办法需要为PowerPC写一些软件,速度较慢。SST公司最近推出的SST55LD017是比较理想的Flash盘的IDE接口控制器,图1是它的功能框图。电路简单、速度快、可靠性高是专用IDE控制器的优点。

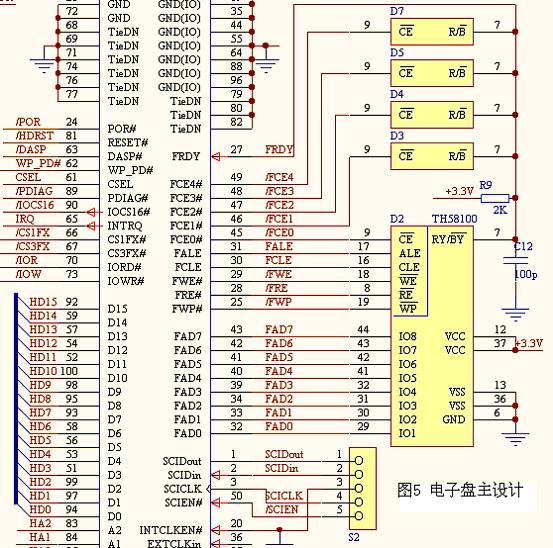

从图中可以看出,它里面包含了一个微控制器和嵌入的Flash文件管理系统。控制器和主机的接口允许数据写入Flash介质以及从Flash介质读出。MCU负责把IDE命令转换成Flash介质操作所需的数据和控制信号。SRAM缓冲极大地优化了主机和Flash介质之间的数据传输。内部DMA直接把缓冲数据传输到Flash介质,越过MCU,提高数据吞吐率。嵌入式Flash文件系统为基于文件的操作系统提供了方便。多任务接口可以对多个Flash介质器件进行读、编程和擦除操作。SCI接口用于重新进行芯片初始化过程和配置ID号,为硬件调试提供方便。对于具体的管脚定义可以参考后面图5的逻辑电路。

三 与非阵列Flash存储介质

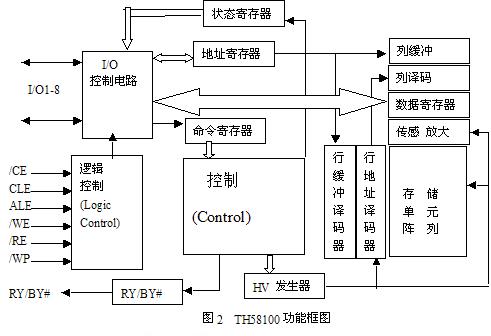

机载硬盘不能使用通常的机械式磁头和磁介质,必须用E2PROM来存储。电子盘只要满足IDE接口格式,读写操作对操作系统是透明的。东芝的TH58100是128M x 8Bit的E2PROM,比较适合做电子盘的存储介质,图2是它的功能框图。

TH58100使用+3.3V电压,其与非阵列安排为 528字节 x 32 页 x 8192块。它里面有一个528字节的静态寄存器,允许编程数据和读出数据在寄存器和存储阵列之间以528字节为单位传输。IO1—IO8管脚既是地址线,又是双向数据线,同时承担命令输入。发出命令后,擦除操作和编程(写入)自动进行。具体管脚可参考图5的电路。

四 电子盘设计

“手中有粮,心里不慌”。掌握了IDE控制器和Flash介质,设计电子盘就很容易。设计时要考虑机载的电磁环境比较恶劣、机械振动要求较高这一特点。下面从三个方面介绍设计的主要部分。

4.1 电源与复位

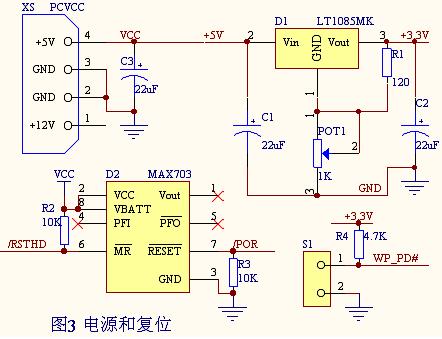

Flash介质只使用+3.3V电源,而IDE控制器同时使用+5V和+3.3V,但PC机及扩展的EIDE接口都仅使用+5V电源。为了和PC兼容,电源一方面来自机载系统,另一方面仍可从PC标准电源传入,VCC = +5V。如图3所示,XS就是PC电源标准接口。使用DC/DC电压转换器,将+5V电压转换为+3.3V,满足IDE控制器和Flash介质需要。机载环境下外供电源极不稳定,经常有长达20ms的瞬间掉电。为保证上电/掉电时可靠复位,不要采用普通的RC复位电路,图中使用MAX703实现可靠复位。上电复位信号/POR接图5的D1.24管脚,使上电和下电瞬间,IDE处于确定的复位状态,拒绝接收主机的误操作命令,避免对Flash介质进行误操作。D2.6腿是手工复位输入信号/RSTHD,允许调试过程随时复位。图3中的WP_PD# 信号接至图5的D1.62管脚,是写保护跳线。

4.2 IDE接口设计

在设计时,既在逻辑上实现了IDE接口,将有关信号嵌入系统总线,又在物理上直接使用了标准的IDE-40芯插座,可以直接连接到PC机硬盘连线,方便软件开发。其设计如图4所示。为保证上电时DMA请求DRQ处于低电平,避免主机错误响应,应该使用5.6K电阻下拉。同样,IORDY使用1K电阻上拉。S2跳线用来进行主盘(Master)和从盘(Slave)设置,断开时将IDE接口设置为从盘,短接时设置为主盘。在复杂电磁环境下,还应该给DRQ串联33Ω的端电阻,给IORDY串联82Ω的端电阻。根据ATA-4规范,应该给数据线HD7下拉10K电阻,使主机能够迅速识别是否安装硬盘。这些措施在图4中并没有体现出来,在工程实践时要特别注意是否采用。

4.3 控制器设计

控制器主设计如图5所示。LD017控制器一边负责IDE接口,一边负责对TH58100存储介质进行读写操作。上电复位信号/POR来自图3的MAX703输出,普通复位/HDRST来自主机IDE接口,同时允许软件复位。主从选择线CSEL在芯片内部已上拉,悬空时做从盘(Slave),接地时做主盘(Master)。当主从盘同时存在时,要将主从盘的诊断信号/PDIAG连在一起。

控制器和存储介质之间有/FCE0--/FCE4五根片选线,可以组成5 x 128MB容量的电子盘。地址、数据和命令复用线FAD7—FAD0,操作时由FALE和FCLE锁存信号区分。其中FALE是地址锁存使能,FCLE是命令锁存使能。图5中的SCI接口(S2)只是示意性质,具体可参考图7电路。

当控制器对存储介质读写时,由操作准备好信号FRDY应答。当该信号为低时表示忙。这个信号是集电极开路(OC)结构,必须有上拉电阻。其阻值可根据信号上升时间Tr和下降时间Tf的要求调整。无论连接几片TH58100,只能有一个统一的上拉电阻,以防止过大的灌电流。

双重写保护设计

机载环境下,电子盘文件系统经常遭受破坏,抗干扰和写保护设计是非常重要的。图3中的S1跳线开路时,写保护信号WP_PD# 处于高电平,经过软件设置可使LD017控制器处于写保护状态。不再执行主机发送的任何破坏性命令,诸如格式化、写缓冲、写扇区、验证式写等命令。当需要装入程序或合法记录飞行状态时,将S1短接并用软件开锁。这是第一重写保护。第二重保护应该设计在LD017控制器和存储介质之间。在图5的D2.19管脚,即TH58100的写保护用10K的电阻下拉,确保上电/掉电瞬间LD017在未知状态时的误操作不被执行。这一措施在图5中并没有体现出来。

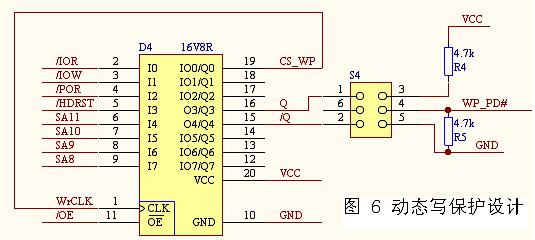

动态写保护设计

在图3的写保护电路中,S1采用手工跳线进行写保护。在运行时只能一直保持在某种状态,例如在写保护模式下,应用程序无法写入。若要写入,必须断电重新跳线。

图6是一种动态写保护改进设计。WP_PD#写保护信号由应用程序控制,根据需要将电子盘设置在可读写模式或只读(写保护)。图中使用GAL16V8实现这种功能,地址和IO读写信号都来自EISA总线,其逻辑核心编程用ABEL描述如下:

… …

EQUATIONS

CS_WP = (!IOW # !IOR) & (SAddr == OurAddr);

Q.clk = WrCLK;

Q.OE = !OE;

Q.CLR = !HDRST # !POR; // 复位.

FBQ = !Q.FB; // 反相输出.

State_Diagram [Q];

State S0 : // 写保护状态.

if (!IOW) then S1;

State S1 : // 可读写状态.

if (!IOR) then S0;

end WrProtect

图6中,当WP_PD# 和Q连接时,上电复位时Q=L,处于写保护模式。应用程序在写盘(文件)时可以这样编写

outp(WrCtrlReg,AByte); // 写该端口,退出写保护模式。

… … // 写盘(文件)操作.

Inp(WrCtrlReg); // 读该端口,恢复写保护模式。

当WP_PD# 和 //Q连接时,上电复位时 /Q=H,处于可读写模式。应用程序在写盘(文件)时和接Q端刚好相反,亦即写端口进入写保护模式,读端口退出写保护模式。

五 调试方法调试软件

“三分设计,七分调试”。硬件设计过程就应考虑调试的方便性。LD017有一个串行通讯接口,可以监控硬件。可以扩展利用。

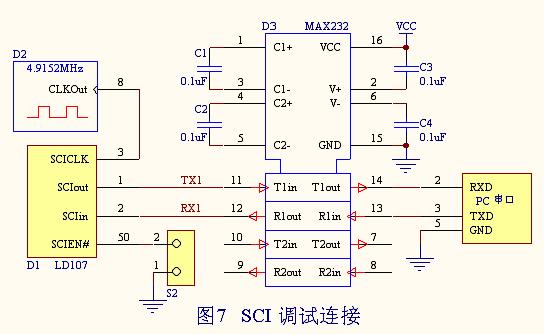

5.1 SCI调试接口设计

通过SCI接口可以得知出错类型信息,更新ID号,改变CHS和PIO模式等,非常有利于调试。其扩展电路具体方法如图7所示。

LD017提供的SCI接口遵从RS232通讯协议,但它是TTL电平。使用MAX232进行电平转换,就可以和PC机的串口连接,进行通讯检测和调试。调试时要将图中S2短接,即接地,使能SCI接口功能。PC串口初始化时配置固定为:

波特率9600BPS Odd Parity(奇校验) 和 1 Stop bit(停止位)。

5.2 调试软件

调试软件除PC机串口和SCI通讯有关命令外,主要集中在IDE接口命令操作。下面是基于OOP技术,采用Delphi语言,为电子盘创建的类(Class)的描述。这个TEDisk类提供可设置的属性(Property)和操作方法(Method),供硬件调试时灵活调用。当循环调用某一方法时,可重复产生特定信号波形,用示波器捕获分析。

const

// IDE 接口命令集.

ChkPwr_CMD = $E5; // or 98H,Check-Power 检查电源模式.

Diagnst_CMD = $90; // Execute-Drive-Diagnostic:驱动器诊断.

… …

ReadSctr_CMD = $20; // or 21H,Read-Sector(s): 读扇区

WriteSctr_CMD = $30; // or 21H,Read-Sector(s): 读扇区

type

TIDEPort = ( idePrimary, ideSecondary);

TDrive = ( drvMaster, drvSlave);

TAdrMode = ( amLBA, amCHS);

// 以下为TEDisk组件(类)正式定义的框架。

TEDisk = class(TComponent)

private

FIDEPort : TIDEPort; // IDE 端口号

FDrive : TDrive; // 主从盘.

FAdrMode : TAdrMode; // 寻址模式.

… …

// CS1FX 信号有效时的寄存器

FDataReg : Word; // 读写,数据寄存器

… …

FCommandReg : Word; // 只写,命令寄存器

// CS3FX 信号有效时的3个寄存器

FAltSReg : Word; // 只读,预备的状态寄存器

FDevCtrlReg : Word; // 只写,设备控制寄存器

FDevAddrReg : Word;

… …

function WaitNotBusy:boolean;

function WaitDRQ:boolean;

public // 公用方法

constructor Create( AOwner: TComponent ); override;

procedure ChkPwrMode; // 检查电源模式.

function Diagnostic(Var Diag:byte):boolean; // 电子盘诊断.

… …

function WriteSctr(SctrNo:DWord;Buf:array of Word):boolean; // 写扇区

function ReadSctr(SctrNo: DWord;var Buf: array of Word): boolean; // 读扇区

… …

published

property IDEPort: TIDEPort read FIDEPort write SetIDEPort default ideSecondary;

property Drive: TDrive read FDrive write SetDrive default drvMaster;

property AdrMode: TAdrMode read FAdrMode write SetAdrMode default amLBA;

… …

end;

implementation

… …

在具体实现时,我们只示意性说明组件二个比较主要的方法,即写扇区和读扇区。其源代码如下:

//-----------------------------------------------------------------------------------------------

// function WriteSctr(SctrNo:DWord;Buf:array of Word):boolean;

// 功能:

// 向电子盘接口写一扇区. 假定采用 LBA 逻辑扇区寻址模式.

// 入口参数:

// SctrNo: 写操作起始扇区号,32-Bit.

// Buf: 写扇区数据缓冲,16-Bit.

// 返回结果

// Result = True: 操作完成.

// False: 操作出错.

//------------------------------------------------------------------------------------------------

function TEDisk.WriteSctr(SctrNo: DWord; Buf: array of Word): boolean;

var AByte:byte;

i:integer;

begin

outp(FSectrCntReg,1); // 设置读写扇区数

AByte := SctrNo;

outp(FSectrNoReg,AByte); // 设置起始扇区号,亦即 LBA7-0.

AByte := (SctrNo and $0000FF00) shr 8;

outp(FCylLowReg,AByte); // 设置柱面号(低),亦即 LBA15-8.

AByte := (SctrNo and $00FF0000) shr 16;

outp(FCylLowReg,AByte); // 设置柱面号(高),亦即 LBA23-16.

AByte := (SctrNo and $0F000000) shr 24;

outp(FCylLowReg,FDriveHead or AByte); // 亦即 Drive,LBA27-24.

outp(FCommandReg,WriteSctr_CMD); // 发写扇区命令.

WaitDRQ; // 等待 DRQ,即 IDE 准备接收写数据.

for i := 0 to 255 do

OutpW(FDataReg,Buf[i]); // 写16-Bit数据寄存器,

Result := WaitNotBusy; // 查看操作结果.

end;

//------------------------------------------------------------------

// function ReadSctr(SctrNo:DWord;var Buf:array of Word):boolean;

// 功能:

// 从电子盘接口读一扇区. 假定采用 LBA 逻辑扇区寻址模式.

// 入口参数:

// SctrNo: 读操作起始扇区号,32-Bit.

// 出口参数:

// Buf: 所读扇区数据缓冲,16-Bit.

// 返回结果

// Result = True: 操作完成.

// False: 操作出错.

//-------------------------------------------------------------------

function TStdIDEPort.ReadSctr(SctrNo: DWord;var Buf: array of Word):boolean;

var AByte:byte;

i:integer;

begin

WaitNotBusy; // 等待上次操作结束.

outp(FSectrCntReg,1); // 设置读写扇区数

AByte := SctrNo;

outp(FSectrNoReg,AByte); // 设置起始扇区号,亦即 LBA7-0.

AByte := (SctrNo and $0000FF00) shr 8;

outp(FCylLowReg,AByte); // 设置柱面号(低),亦即 LBA15-8.

AByte := (SctrNo and $00FF0000) shr 16;

outp(FCylLowReg,AByte); // 设置柱面号(高),亦即 LBA23-16.

AByte := (SctrNo and $0F000000) shr 24;

outp(FCylLowReg,FDriveHead or AByte); // 亦即 Drive,LBA27-24.

outp(FCommandReg,ReadSctr_CMD); // 发读扇区命令.

Result := WaitDRQ; // 等待 DRQ,即 IDE 准备接收好数据.

if Result then

for i := 0 to 255 do

Buf[i] := InpW(FDataReg); // 读数据寄存器, 16-Bit.

end;

在上面读写程序中,我们每次只指定了一个扇区数,在实用程序时应该将扇区数作为一个参数传递。代码中使用的Inp、OutP、InpW、OutpW等I/O操作函数是使用嵌入汇编实现的工具性函数,例如 OutpW和InpW的实现过程如下:

procedure OutpW(Port,Value:Word);

asm

MOV DX,Port

MOV AX,Value

OUT DX,AX

end;

function InpW(Port:Word):Word;

asm

MOV DX,Port

IN AX,DX

end;

其它细节不再叙述,对源代码有兴趣的读者,可直接和作者联系。

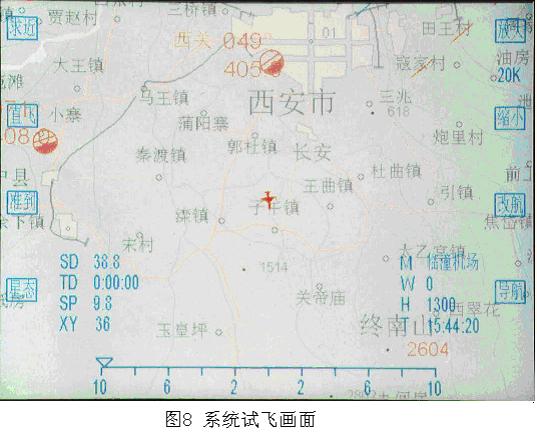

六 结束语

按照上面原理设计的电子盘已经通过装机试飞,图8是试飞的一个画面。试飞证明,电子盘逻辑设计合理、可靠,通过了机载设备所需的各种严格实验,已经开始投入使用。我们相信,随着第4代飞机性能提高,一定有能力保卫祖国领空和领海的安宁与祥和。“落霞与孤鹜齐飞,秋水共长天一色”的美景永存。