EDA厂商各自蓄势 备战下一代工艺节点之设计工具

无论是在第45届DAC(设计自动化会议)上亮相,还是近期在中国市场上做出新动作的EDA厂商,有心之人都能发现他们对下一代工艺技术上设计工具的热衷。为应对在新工艺节点上的低功耗设计、软硬件协同设计、仿真等问题,众多EDA厂商投身到设计工具的积极创新大行动当中。

Cadence联合客户开发系统级综合产品

当许多EDA厂商着力表现在65nm和45nm上的研发成就时,老牌EDA厂商Cadence公司对电子系统级(ESL)综合产品表现出高度重视。Cadence公司总裁兼CEO Mike Fister指出,Cadence目前投资开发的技术在32nm~22nm工艺节点上,Intel使用的一些高性能45nm技术和45nm测试技术也是基于Cadence的工艺技术。他说,“但是我们强调的价值是跳出过去的一套价值考虑方式,要用前瞻性的眼光去看问题,我们看重对客户未来的影响以及对客户的承诺。”

Cadence公司总裁兼CEO Mike Fister

基于前瞻性的考虑和对客户的承诺,从ESL设计考虑如何提升客户的生产力是Cadence当下所欲强调的。C-to-Silicon Compiler是这一考虑的其中一个力作。在Cadence日前的CDNLive!系列全球性技术会议上,Cadence公司高级副总裁兼首席技术官Ted Vucurevich如此推介这一力作: “这一技术由大量来自客户的投入开发而成,例如Hitachi和Renesas。这种高阶综合产品能够让设计师在创建和复用系统级芯片IP的过程中,将生产力提高10倍。”

C-to-Silicon Compiler中的创新技术成为沟通系统级模型之间的桥梁。系统级模型是用C/C++和SystemC写成的,而寄存器传输级(RTL)模型通常被用于检验、实现和集成SoC。这种重要的新功能对于很多公司非常重要,比如那些开发新型SoC和系统级IP用于消费电子、无线和有线网络市场的公司。C-to-Silicon Compiler独特性来自三个方面:其一是嵌入式逻辑综合功能。这一功能使用Cadence Encounter RTL Compiler全局综合,以确保高精确性和高质量的执行结果用于混合控制和数据分支的设计;其二是behavior-structure-timing数据库提供可以实现真实的增量综合。例如,只重新综合设计更改的部分,而其余部分不动。这显然使设计时间大大缩短。最后是C-to-Silicon Compiler生成RTL的快速时序精准的硬件模型,使用Incisive硬件模拟和Palladium/Xtreme仿真加速产品进行快速映射到RTL验证。

Ted Vucurevich认为,也许C-to-Silicon Compiler不能“do all things”,但是它可以让客户减少系统规格与设计实现之间的反复,并为IP创建与复用提高设计师的生产力,这些在消费电子、无线和有线网络市场是特别重要的。

Cadence在CDNLive!上强调,2008年Cadence在中国有四个重大目标。第一是节能,就是加强低功耗设计的能力,这是Cadence基础的技术;第二是创新,Cadence把公司研发人员创新的结果带给客户;第三是和谐。EDA产业是整个半导体设计界的一部分,Cadence和客户一起做出完整的解决方案,把EDA的工具和IP等合在一起。第四是与客户共赢。Mike Fister 说,“我们现在的着重点就是要让我们的工程技术人员使得他们科学理念能够不断的化为现实。大家可以互相讨论和交换经验,通过鼓励创新来实现它,就像中国的奥运一样。”

Magma志在先进工艺市场

2008没有多少利好消息。油价飙升、物价上涨,这些不仅让每个国家的政府头疼不已,更让众多的公司对当下的投资十分谨慎。然而就在不久前,EDA厂商Magma(微捷码)首席执行官Rajeev Madhavan极具信心地主持了该公司在北京和上海的办公室扩展开幕仪式,并宣称这标志着Magma致力于在中国建立世界级运营规模的蓝图已经获得最新的进展。Magma在北京和上海两地的办公室面积增加了1,800平方米,达到约140%的增长。与此同时,Magma还揭开了与中国大学合作计划的序幕,旨在与中国本地大学进行合作以培养工程技术人才后备队伍和促进研究工作,提供课程教材、软件以及专门的支持,向领先的自动化研究实验室提供援助。Rajeev说,“随着半导体工艺向65nm、45nm制程的发展,我们能够为未来的IC设计产业做的更多。”

Magma首席执行官Rajeev Madhavan

以一体化设计平台为特点的EDA工具

虽然Magma的工具在无线设备芯片的设计中占据了市场份额的85~90%,但由于其工具集中在65nm、45nm及更高级的制程上,Magma对未来的美好前景志在必得。在DAC大会上,相比于其他大的EDA公司来说,Magma表现格外努力和积极,其展台处不时聚集工程师或客户驻足与Magma工作人员交流。

Magma的所有产品都具有一体化的设计平台,从底层的数据结构开始,其所有的工具都紧密地集成在一起,这是其产品的一大特色。它是该公司自己设计的针对65nm~45nm的平台。与以前需要买很多不同的工具,并把它们拼在一起才能做一个完整的flow相比,Magma的工具是从RTL到GDSII可以一步做下来,使产品的研发与科学研究过程变得容易很多。该平台的核心技术是其专利的统一数据模型。

其产品基本上涵盖了所有的IC设计体系。比如,Talus是针对数字信号和混合信号的设计工具,TITAN是针对模拟信号的设计工具;混合信号验证工具则有Quartz、FineSim以及Quickcap等。

作为BlastFusion的升级产品,Talus的主要特点除了一体化的RTL-to-GDSII系统外,另外一个特别突出的特点是multi-corner驱动和异敏(variation awareness)驱动以及这些驱动的优化技术集成到RTL-to-GDSII的系统中。这样,使用竞争产品做一个项目,如果10个工程师十个月能做完的话,在同样的时间里,使用Talus可能只需要三四个人就能完成。

一如另一家EDA工具提供商Solido公司CEO Amit Gupta所说,现在的IC设计目标不仅仅是功耗或时序的问题,很多时候是在功耗、时序和尺寸之间进行权衡和平衡,Magma具有MultiDVD、MTCMOS、Clock Gating和Power aware等技术,能够在规定的范围内给出最小的功耗。

混合信号验证工具同样体现了Magma的一体化设计平台概念。Rajeev Madhavan指出,目前市场上的验证工具基本上都是在设计流外面进行验证,在GDSII实现之后才运行DRC检测,这时发现问题再回过头去解决,绕了很大的弯路。QUARTZ、FINESIM、QUICKCAP则是采用在周期中验证的方法,在逐渐设计收敛过程中做DRC验证,发现问题时可以随时修改。一体化概念同样渗透于时序验证和提取方面。

中国大学计划培养未来市场

正是由于Magma工具的综合性,到目前为止,中国本土公司使用Magma工具的还很少。一方面它们大多还停留在.13µm、90nm的设计阶段,更多需要的不是综合性工具。相比之下,印度大多在65~45nm工艺节点上设计水平要先进得多。Rajeev指出,在印度有很多跨国公司首先提出更高工艺节点的设计需求,带动了印度的毕业生做最尖端的设计。在中国很多设计活动主要还是由中国自己的公司驱动的,但它们的工艺不是很前沿。“Magma在印度理工学院培养出了很多设计师,此次在中国的大学计划,我们也希望能够为中国市场培养出有经验、有能力的设计师。”

虽然在中国的比例并不算多,但Magma在亚洲的营收仍然占到16%,而且中国市场的成长很快,每年的营收成长达一倍。Rajeev说,未来先进的生产工艺会逐渐向中国大陆转移,设计人员将能够直接跳过90nm直接进入65nm和45nm制程,这对Magma来说是个必然的机会。

Mentor Graphics多方位强化EDA工具

Mentor Graphics也在全方位强化自己的EDA工具,以期在未来的65nm、45nm以及更先进工艺节点的市场中继续巩固领导地位。

Olympus SoC确保设计功耗和信号完整性

传统的布局和布线工具面临着效率不高的挑战。从应用上看,现在的布局和布线解决方案已经经过了10~15年的时间,这些方案具有以下几个特点:主要是针对150~180nm制程;在同一时间,分析和优化引擎用于实现单角单模(one corner/mode);布线引擎并不是用来处理复杂的DRCs/RDRs;在设计执行期间制造问题没有得到解决;架构不够灵活。

Mentor Graphics副总裁兼设计到制造部门总经理Joe Sawicki认为,面向下一代的布局布线系统对EDA工具提出了新的要求,比如具有新的时钟分析架构、新的布线方法,以及具有可扩展的数据模型等,以实现功耗削减、优化DFM、运用分层/平面设计方法进行100M+门以上的设计。

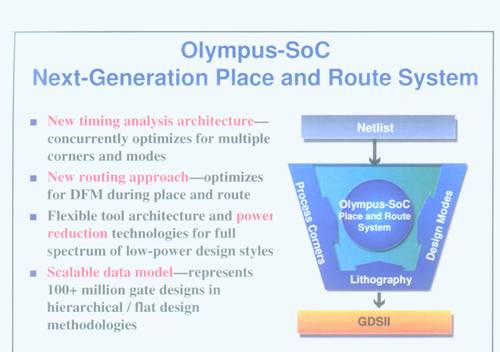

通过对EDA公司Sierra的并购,Mentor Graphics在从网表到GDS-II的实现工具Olympus-SoC与DFM工具Calibre LFD之间建立了协作运行流程,使上述传统工具下存在的设计问题迎刃而解。Olympus SoC是专门针对65nm/45nm制程的布局布线系统(图1),它集成了由光刻驱动的布线技术,可同时进行多角多模的分析和优化,能够处理100M+门的大型设计。工具中内置的多角时钟树综合和多角多模信号完整性技术能够确保设计获得令人满意的功耗和极佳的信号完整性。Joe Sawicki指出,使用Olympus SoC与不使用时相比将提高时钟和功耗设计效率,使通过拐角的时钟变异减少40%,缓冲区面积减少50%,总设计面积减少18%,时钟功耗减少30%,动态功耗减少20%。

图1 Olympus SoC下一代布局布线系统

提供全方位的验证工具

事实上,系统级的功能错误是现在导致芯片重新投产、影响产品上市时间和收益率的重要因素。同时,在集成电路从ASIC与SoC并存时,进行“层次化”版图验证的工具就显得十分必要。

Mentor Graphics提供的Scalable Verification验证方案,可以完备地解决系统设计和验证中可能遇到的数字、模拟、固核、软件的集成化验证,同时可以覆盖在设计的模块级、子系统级以及完整系统等不同阶段所需要的验证。

在物理验证方面,现代IC设计中的设计规则正在迅猛增加。在180nm制程时,所涉及到的规则数量为500个左右,到了90nm阶段,规则数已经超过了1000个,在45nm制程,将会涉及到更多的设计规则。与此同时,设计规模的日趋庞大、错误数量及验证过程的反复次数增多,总周期时间也相对变长。针对这些问题,Mentor称,其新的Equation-basese DRC将解决设计团队的验证需求。

Equation-basese DRC主要使用3个DFM工具:关键面积分析(CAA),走线路径友好设计(LFD)以及平面化学机械抛光(CMP)制造平台。其中,LFD可在设计初期对工艺变化进行管理。设计人员可以运行模拟程序来观察版图在特定光刻工艺窗口下的印刷情况,以实现设计目标。Calibre LFD还会计算出一个设计变化指数(DVI),用来测量设计对工艺变化的弹性,帮助设计人员挑选出对工艺变化敏感度较小的方案。

Mentor相信,客户的成功和满足未来挑战的发展路线将使其在EDA市场的领导地位得到加强。

CebaTech力推ESL工具应对业界设计挑战

随着半导体产业的发展,IC设计所能支持的功能越来越复杂,设计过程本身已经成为现代IC实现终极应用潜力的一大障碍。无论是SoC还是ASIC,亦或是FPGA,任何一个复杂的芯片产品研发的投入都很巨大,多步骤的研发过程给产品的延迟交货和研发失败提供了多种机会。

CebaTech在45届DAC大会上力推其C2R编译器解决方案,该方案正是为应对现代设计挑战而设计。这种ESL工具把未定时ANSI C作为它的HDL。CebaTec通过三种方式解决问题:其一是支持ANSI C语言的强大能力;其二是支持规模从小到大、各种复杂规模的设计;其三是在C语言环境下,通过在设计进程的前端进行功能验证,能够实现95%的测试覆盖率。

C2R编译器利用条件指令将序列源代码映射到硬件微架构。与此同时,源代码与任何标准的C语言编译器保持兼容,并且它允许设计者利用标准的软件开发工具来加速硬件设计的功能验证。

在线性环境中,有了ANSI C语言的支持,C2R编译器能克服存在于序列软件模型与并行硬件设计之间的“语义鸿沟”。这不仅能够使原设计快速执行,也允许IC设计师相对容易地从已存在和已经验证过的软件中得到硬件架构。有多线程操作系统支持时,ANSI C能够通过外部指令提供并行架构。

利用ANSI C编译器,可以进行1G/10G TCP/IP卸载芯片的设计、DES/3DES/AES加密芯片的设计等,在无线应用、视频/图像处理领域亦能发挥不菲效果。

CebaTech不仅为半导体设计开发先进的ESL工具,并使用这些工具创建新出现的市场机会中具有高附加价值和具有一定复杂性的IP。其中包括面向网络和存储应用的IP如GZIP/GunZip等。这些IP能够进行基于标准的无损数据压缩和解压缩,并实现极好的压缩比。

另外,CebaTech客制化的设计和组态等IP服务能够满足特殊的应用需求。

EVE系统仿真器加速软硬件联合验证

在DAC会议上,致力于提供低成本硬件辅助校验产品的EVE公司展台前摆出了两台游戏机,几个年轻人围在游戏机旁兴致勃勃地打游戏。EVE大中华区总经理陶定良介绍,游戏也是该公司瞄准的市场之一,微软Xbox 360设计过程中使用的正是EVE的仿真工具。

早期的仿真工具非常昂贵,体积也比较大。随着工艺的进步,软件设计出错带来的损失令设计团队越来越难以承受。陶定良认为,用硬件辅助软件进行模拟加速设计可以帮助减少软件设计出错,用硬件平台验证软件设计的正确性是未来的发展趋势。

图2 EVE ZeBu AHB主机事务处理器

目前EVE已经推出板级ZeBu-Personal仿真器和独立的ZeBu系统仿真器。ZeBu-Personal与ZeBu-UF以及ZeBu-XXL属于同一系列,都可用于FPGA原型验证,其中ZeBu-XXL具有多插槽。ZeBu-AX是基于多核客制化处理器ASIC技术的仿真工具,用于RTL不稳定时的仿真测试,且可进行多次修改。与针对Verilog、SystemVerilog、VHDL和混合语言设计的单纯仿真相比,ZeBu-AX可以提供大约1000倍速度的仿真加速。

陶定良指出,过去的仿真是在Pin level级别,速度很慢,测试向量的信息交流非常复杂。现在的仿真器已经实现事务处理(Transaction level)级仿真,交流一次信息可传送大量数据,传送速度很快。

ZeBu AHB主机事务处理器是EVE公司ZeBu系列产品之一(图2)。该产品可以在最高的性能上验证基于AMBA2的设计,在流片之前完成对设计的测试和调试。ZeBu AHB主机事务处理器包括硬件和软件两部分。通过ZeBu事务架构提供的信息端口,硬件和软件部分可以互相通信。硬件部分驱动AHB事务到DUT的AHB总线,软件部分包括一套库功能,以产生和执行AHB事务。处理器支持32位、64位和128位总线宽度。

随着电子产品中软件所占的比重越来越大,EVE在扩大产品应用上也有所动作。它与CoWare、Tensilica等公司建立了很好的合作关系,以使更多的客户能够使用到EVE的产品。

Solido第二代统计偏差设计工具助力提高成品良率

在IC设计过程中,统计偏差常常导致产品失败。模拟/混合信号、客制化数字和存储IC设计师被越来越短的产品设计周期压得喘不过气,低电压、低功耗的时代需求也增加了设计偏差产生的几率。Solido公司指出一个事实,即大多数产品的流片都具有严重的工艺偏差问题。如何尽快发现这些导致设计失败的原因并对之进行设计改动?

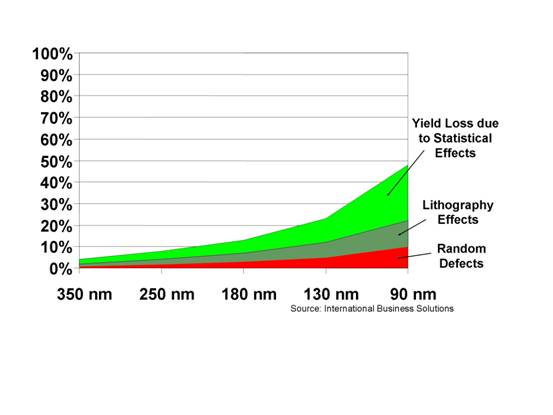

Solido公司CEO Amit Gupta认为,半导体工艺技术已经发展到了65nm甚至45nm,电路设计技术也在发生着突飞猛进的变化,但是工艺设计偏差的设计工具显然并没有跟上时代的步伐,但实际上,工艺的进步对产品良率的影响也在逐渐变大(图3)。Monte Carlo仿真(一种静态时序分析)确实能够生成设计的参数成品率,但问题是,他们在运行仿真和获得偏差分布以后,并不能确定到底是设计的哪个部分造成了这种分布。而且,Monte Carlo仿真是耗时而又缺乏效率的。

瞄准先进制程上的IC设计,Solido在推介其第二代统计偏差设计工具SolidoSTAT。在SolidoSTAT下,工程师可以很快地分析由于统计偏差导致的设计失败,并缩小和锁定设计失败的原因。SolidoStat中提供了采样、电路增强器、SolidoStat TradeoffAnalyzer等引擎。

Amit Gupta认为,在晶体管级设计时,工程师要处理成百上千个变量,这需要达成一种平衡,如增益、相位裕度、CMRR、功耗、偏移电压以及增益带宽、晶体管的稳定时间等。最重要的还是环境的影响。另外,晶体管级工程师还必须考虑到一些全局统计变量,如长度增量和器件变量等。这样,要处理的变量实际上更多。

图3 统计偏差严重影响成品良率

在上述情况下,为保证达到成品率界限,工程师通常会在最差工艺拐点的边界内作设计。但也要付出相应的代价,比如损失性能、功耗或其它指标。“SolidoSTAT就是帮助工程师在电路实现成品率的同时,获得更好的性能,降低功耗,这也是我们值得骄傲的地方。”

新工艺节点上的EDA厂商格局酝酿变局

可以想见,全球的经济低迷对半导体产业同样造成了影响。这种情况下,我们可以感受到EDA厂商这个时候蓄积力量、期待后势发力的气氛。也有业界人士表示,EDA产业的格局正趋于稳定,而未来的格局可能会在向65nm/45nm工艺节点变化时发生。我们感到这个变化已然近在眼前。而能够抓住这种变化所带来的发展机遇的,只能是那些充满创新的公司,不管它们是被收购还是进行收购。