26路脉冲计数设计 仿真波形图分析

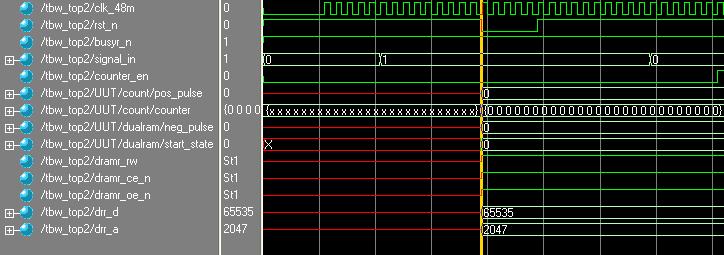

1、复位信号rst_n下降沿到来,大部分寄存器从不确定状态x清零。因为此时脉冲计数使能信号counter_en还没有拉高(使能),所以即使输入脉冲signal_in有一路信号出现下降沿,但是仍然没有写入dual RAM的操作。

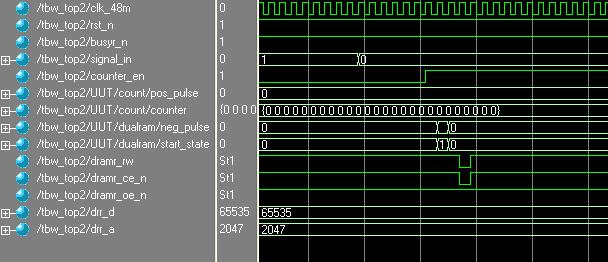

2、当counter_en拉高使能后,立刻出现了一个dual RAM写操作(start_state=1)的时序,是因为signal_in的三个寄存器siganl_in_r0/r1/r2复位初始化时是处于全1状态(这是为了考虑不出现误检测到上升沿而把脉冲计数器加一的错误)。而此时只是往65535地址写入2047(更改后为往0地址写入0数据),这对我们的设计结果没有影响。

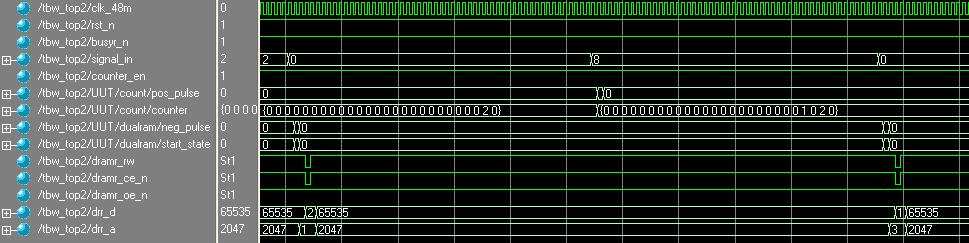

3、正常计数开始:波形中,信号signal_in从0到2跳变时,说明signal_in的第1bit上有上升沿脉冲道来,此时pos_pulse的第2bit也拉高1个时钟周期以便脉冲计数单元counter的第1个16bit寄存器进行加一计数。然后在黄线处是signal_in第1bit的下降沿(neg_pulse=1保持一个时钟周期),在它以后的几个时钟周期里往dual RAM的地址1写入脉冲计数值1。

以下是同样signal_in的第1bit再出现两个脉冲后,分别在脉冲的下降沿往dual RAM的1地址写入脉冲值2和3。

相关推荐

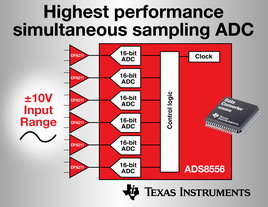

德州仪器推出同步采样ADC

2009-10-26

在线研讨会

焦点