利用CAP实现超宽带流媒体访问控制器

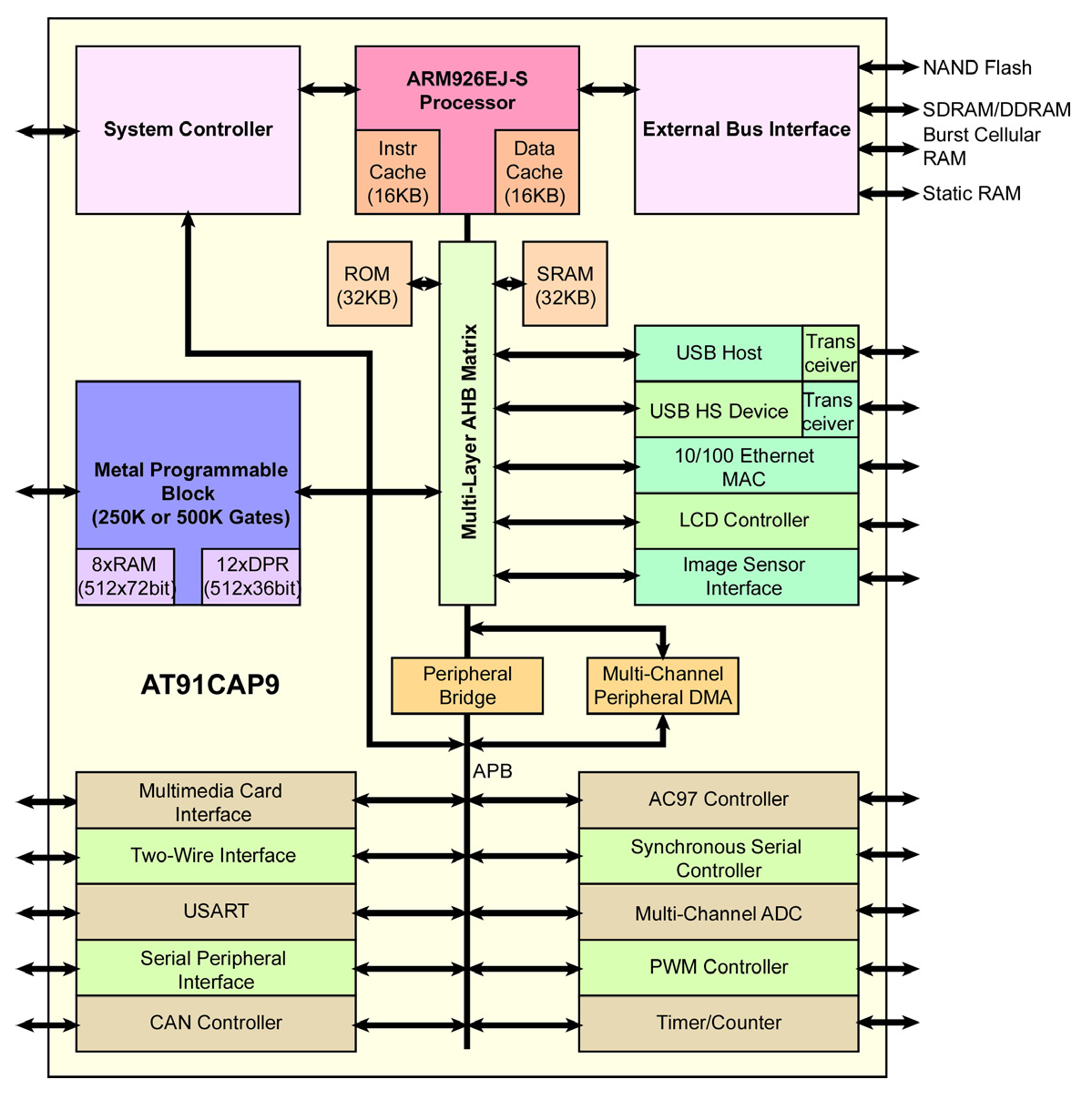

图 5 所示为 UWB MAC 架构的简图。图中上半部分是MAC-PHY 接口 (MPI) 与 CAP的 AMBA 先进高性能总线 (AHB) 之间的快速数据路径。外部存储器查找通过 RX 和 TX 端点 (Endpoint) 实现。每一个端点都包含一个地址指针,用以确定 AHB 主设备所需的起始地址、终止地址和存储器读写位置。每一个表或存储区域都需要一个端点。MAC PHY 接口(MPI) 是到 UWB 物理层的接口,符合 ECMA-369 标准 [注2]。

TX Data Stream TX数据流

TX 数据流 (见图6) 是将所有帧从应用发送到 PHY 的高速数据路径。这个数据源可能是 AHB 寻址空间的存储空间或单个寄存器。AHB 主设备的作用类似于 DMA,在收到会请求后,TX AHB主设备便会从存储器缓冲区读取数据并传送给MPI接口。当总线获得允许,主设备就开始进行连续有序的传送。突发流量大小、起始地址、方向和包络边界(wrap boundary) 都通过AHB 主设备配置接口由 TX 端点提供。若 RX AHB 主设备和 TX AHB 主设备都需要传送数据,TX AHB 主设备拥有优先权。TX 端点模块根据自己的配置情况和存储段逻辑所提供的信息,对 MAC 帧头字段进行更新。MPI 接口负责根据调度器更新PHY 报文头 (header) 字段 (信息包含在 MAC 和 PHY 头字段中)。报文头信息由状态/报文头 (Status/Header) RAM 提供,后者是 CAP 紧密连接的存储模块的一部分。此外,也可以无需经过报文头生成过程,而报文头直接由来自存储器的用户数据提供。

这个端点会实现与调度器 (scheduler) 的握手接口,而状态/报文头 (Status/Header) RAM 则存储多个端点的状态和配置信息。如果调度器请求一个帧,FSM 便开始从 RAM 往AHB 主设备加载配置,然后加载状态和配置寄存器。如果由软件设置,该端点此时会把帧头从 RAM 发送到 TX STREAM 总线。接着,FSM 启动 AHB 主设备,把数据从外部存储器传送到 TX STREAM 总线。当发送操作成功结束时,调度器会发出一个成功的命令,这时,FSM 会把状态信息写回 RAM。如果帧发送不成功,便会发出一个错误命令来阻止FSM写回状态信息。如果采用B-ACK,调度器可能在成功或错误命令被发送之前就发送请求命令。

RX数据流

由图7可见 RX 数据流是由 PHY 接收并发送给应用的所有帧的高速数据路径。当帧RX、TX 逻辑 (FRT) 从 PHY 接收到一个帧时,便会将其存储在 FRT 的缓冲器中,直到它确定该帧的地址;而 CRC32 校验码也匹配。这时,FRT 就会通知调度器有新帧到来。RX 端点负责配置 RX AHB主设备,然后数据会通过AHB主设备从FRT缓冲器发送到存储器空间 (或 AHB 地址空间内的寄存器)。如果成功,RX 端点可以在发送数据之前抛弃帧头;或者,端点可能完全抛弃接收到的帧。

AMBA AHB主设备负责把 RX 端点的数据存储到外部存储器中。当总线允许时,主设备便开始连续有序的传送。突发流量的大小、起始地址、方向和包络边界都通过AHB主设备配置接口由RX 端点提供。

帧接收发送逻辑 (FRT) 为RX 端点提供帧信息,比如 UWB 寻址、配置和端点状态。当 FRT 通知有新帧被接收时,FSM 便开始搜索匹配的滤波器。如果发现适当的滤波器,端点 FSM 从配置 RAM 向 RX AHB 主设备加载 AHB 配置数据。然后,这个帧会被发送到一个外部存储器,而 RAM 内的 RX 计数器字段将被更新。另一种方式是,端点不搜索适配的滤波器,而由调度器提供固定的端点数目。当帧/链路只以时间来区分时 (例如DRP),这种方式是很有用的。这些端点的激活可以与自动搜索和调度器预选无关。只需把帧顺序地存储在 EBI 数据存储器中,便可以重新组装碎片帧,而其中只有第一个帧存储它的帧头。这种重组装工作只有在端点被设置为从单个地址接收帧时才起作用。本设计尚不支持群发端点和无序发送。要完全支持重新组装,需要一个中段存储空间 (不论是在内部还是外部)。

帧接收发送逻辑 (FRT)

图8为FRT 接口的简图,利用一个 CRC32 逻辑在这些帧接收或发送期间实时计算它们的校验和 (checksum)。FRT 中的 FSM 从调度器接收命令,并启动 RX 或 TX 操作。此外,它还控制发送帧的附加循环冗余校验码 (CRC)。FRT-FSM 的状态通过 FRT 状态接口报告给调度器。FRT-FSM与调度器锁步,并由命令行与状态寄存器所控制。

通过 FRT 接收到的数据会被存储在 FRT 接口的RX 缓冲器中。只有在确定 CRC 和帧的目标地址有效之后,FRT-FSM 才通知 RX 控制模块新帧已到达。接着,RX 控制逻辑读取新接收到的帧的帧头,并向 RX 端点输入大小、类型和源地址等信息,而 RX 端点控制从RX 缓冲器读取数据。RX缓冲器中的一个附加位则会示意帧边界同步。

TX 数据将根据调度器提供的配置信息被格式化,然后数据会存储在 TX 缓冲器中。TX 缓冲器的主要用途是补偿 EBI 和 AHB 造成的存储器数据读取延迟。当 FRT-FSM 发出一个 TX 操作命令时,TX 缓冲器便会向 FRT 发送数据,并在发送期间计算出CRC,再附加在数据流之末。