减小ESD引起的停机时间

半导体常常因静电放电而失效。弄清楚失效的根源并遵守设计规则,就有助于避免这种失效。

(静电放电)是导致电子器件失 效的主要原因,它可以在任何阶段——从制造到测试、组装、生产、现场运行以及现场 PC 装配等——影响电子器件的功能。专家估计,1994 年全世界电子行业因 ESD 造成的损失超过 900 亿美元(参考文献 1)。ESD 的发生原因是电荷在某一表面的累积,如摩擦生电。但是,由于电子产品的快速小型化,导致器件的几何尺寸缩小,其中包括层厚度,因此这些高密度器件就很容易受到很小 ESD 造成的损坏。

造成ESD的人为原因包括人造地毯、人造地板、羊毛服装、尼龙服装、塑料家具、塑料扇叶的风扇、普通塑料容器、带塑料吸嘴的去焊器、不导电的鞋、人造地板垫、玻璃纤维容器、普通塑料袋以及类似的。使用塑料零件的机器也可以成为静电的来源,因为塑料部件之间的相互摩擦会积累电荷。设备产生的高强度电磁场也会在邻近元件中感应产生静电荷。

静电是一种看不见的破坏力,会对电子元器件产生影响。ESD 未必总造成元器件的完全失效;它会造成一般测试无法检测到的元器件潜在缺陷。这种“脆弱”的元器件在系统工作期间,在恶劣环境条件下,更可能在现场发生失效。在制造、储存、运输、包装、组装、测试阶段采取一些简单的预防措施,再适当地设计电路,就可以减少由 ESD 造成的损坏影响。对于半导体器件来说,如果有一个强电场施加在器件结构中的氧化物薄膜上,则该氧化物薄膜就会因介质击穿而损坏。很细的金属化迹线会由于大而损坏,并会由于浪涌电流造成的过热而形成开路。PN 结的失效可能是由于“电流拥塞”效应而引起的,这种效应在大电流通过 PN 结造成大电流密度时发生。ESD 造成的潜在缺陷可能使器件在以后更容易损坏,并且可能使器件时好时坏。

ESD 与闩锁效应

ESD 和相关的电压瞬变都会引起闩锁效应(latch-up),这是半导体器件的主要失效之一。在闩锁情况下,器件在电源与地之间形成短路,造成大电流、EOS(电过载)和器件损坏。CMOS 器件之所以因闩锁效应而特别容易损坏,乃是因为电感会在器件的寄生电容中累积。另外,氧化物材料中任何原子一级的缺陷都会降低氧化物层的介电强度,使器件很容易因静电电压而失效(见本文网页版的附文《ESD 闩锁效应的模型》)。

电子系统中常见的 ESD 问题是通信接口器件,如 RS-232 驱动器和接收器的失效。这些器件在 ESD 脉冲通过人们频繁插拔的电缆互联传播时,在电缆接触到未端接连接器的带电表面时,就会损坏。当这些 ESD 脉冲的频率超过 1 GHz 时,PC 电路板的印制线和小段电缆就会像天线一样,接收这些干扰信号。

图 1 示出了最近对一种频繁失效的 CMOS 数据收发器 IC 进行的 ESD 闩锁效应调查的结果:在某些情况下,IC 封装带电,并烧毁了下面的电路板。为了确定故障的原因,用一台记录仪器监视电源和 RS-232 收发器的输入端。记录的波形显示出在收发器器件的输入端和电源脚有短时的电压瞬变。当这些瞬变电压迫使寄生 PNPN 结构导通时,就发生闩锁效应。一旦寄生的 SCR 导通,SCR就是电源通过器件到地的一条低阻通路。在这样的条件下,通路中的电流很大,从而导致器件中因热过载而热耗散异常。过度的热过载会使塑封外壳升温并开裂。

从设计开始控制 ESD

防止由ESD 引起的失效的第一步是电路设计。要从ESD出发,选用适合于应用需求的器件。对采用不易受 ESD 损坏的元器件的电路进行恰当的设计,就可减少电路板和系统现场失效的发生率。例如,决不因其速度较快而选用某个器件,而要按所需的工作速度来挑选合适的器件。高速逻辑转换会产生高频电磁场,干扰电路板上的其它器件。高速器件使用不当,会因开关引起的有害辐射而添麻烦。

在实验室中按规格测试和验证合格的设备在实际现场条件下可能会出现问题。只有预计到现场可能出现的问题,才能按照在各种工作环境中正常工作这一要求来进行电路设计。这种情况对处理 ESD 问题特别适用,因为这样的问题可能会因现场搬运PC组件时不遵守注意事项而发生。为了解决ESD问题,在产品设计时采取预防 ESD 损坏的措施是必要的。即使某个器件具有内置的保护网络来防止 ESD 损坏,也应在为受损坏的应用场合采用外部元器件进行更高级别的防护。

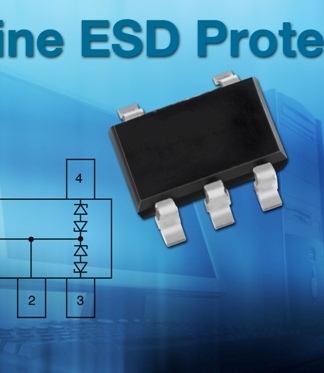

一种众所周知的 ESD 能量抑制技术是在电路的关键部位使用瞬变抑制二极管。这样的器件基本上是快速响应的电压箝位器件。当 ESD 或其它因素产生一个过压瞬变脉冲时,瞬变抑制器就按照其额定值将电压箝位于一个安全电压值,以保护瞬变抑制器后面连接的器件。应根据器件能承受的预计瞬时功耗,仔细地选择瞬变抑制器的功率承受大小。

一种可在电路输入级使用的简单的ESD 瞬变抑制技术,就是将一个磁珠串在输入引线上,并在输入引线和地之间接一只容量很小的电容器。图 2 示出了磁珠的等效电路。输入端的 LC 电路起滤波器的作用,将 ESD 瞬变的能量分流入地。当使用瞬变抑制二极管保护任何输入端或输出端时,要使瞬变抑制器尽量靠近这些端子。很长的导线和电路板印制线都有寄生电感,当 ESD 瞬变脉冲进入电路时,寄生电感就会产生电压过冲与振铃问题。

你可使用 CMOS 布局技术来防止闩锁效应,因为CMOS布局技术可监控 ESD 瞬变会进入器件的各部位:器件的电源引脚、输入引脚和输出引脚。你应降低晶体管(PNP 和 NPN)的增益,并提高闩锁效应的阈值,方法是加大器件结构中 P 沟道 Tub 与 P 沟道漏极之间的间隔。在电源和 p-tub 上连接 p+ 和 n+ 保护环也可以降低晶体管增益,提高闩锁效应的阈值(图 3)。防止闩锁效应的其他工艺技术有:提高阱深度以减少寄生晶体管的增益;采用绝缘衬底(如蓝宝石硅)以降低 tub 和衬底中的电流,;在每个阱下面采用埋层或外延层(图 4)。

你也可以用良好的电路设计技术来减少 危害和与 ESD 有关的电子失效。元器件选用得当和关键部位使用电路级技术(保护网络)均可减少ESD的种种影响。良好的接地与电路板布线技术;在装配、生产和测试时小心取放对 ESD 敏感的器件;在包装和运输器件和组装电路板时采用适当的防静电包装,这些措施都可减少失效。电路屏蔽得当也可以减少 ESD 的影响。

电路板布局会影响 ESD

你如果使用布局和布线都很好的电路板,就可以显著减少 ESD 问题的发生率(见附文《实现 ESD 故障最小化的电路设计原则》)。每一电路都因为有不同类型的元器件和而存在有静电通量线和磁通量线。如果电路板布线围住很大的环形区,则导电通路就会围住较大的磁通量,由于环路起天线的作用,较大的磁通量又会在环路中感应产生电流。这种环路电流会产生影响电路中元器件的干扰电磁场。减小环路区的方法是使电源线和地线尽量靠近在一起。图 5 示出了典型的电源线和地线形成的环路区。

要在电路板设计中采用低阻抗地线,以便任何 ESD 电流都能很容易地流入地,而不是经过电子器件的其他低阻通路流入地。一个接地区域,最好是一个接地层,均可降低 ESD 的影响,因此,你应将电路板上未用区域都变成接地层。使信号线靠近地线也可减小环路面积,并可将大环路引起的 ESD 问题减至最少。具有独立接地层的多层电路板则更为可取。

在电路板布局时,敏感电子元件要远离潜在的 ESD 源,如变压器、线圈和连接器。这些潜在的ESD源会积累电荷或产生杂散的电磁场,从而导致元件损坏。对线圈、变压器和类似元件进行屏蔽,以抑制这些元件辐射的电磁场,这是明智之举。要在很长的信号线之间布放一根地线,以减小环路面积。你把敏感电子元器件放在远离电路板边缘的地方,就可避免 ESD 偶然损坏这些元器件;因为这样做可避免人体接触和可能由ESD引起的损坏。

许多由 ESD 引起的现场失效是由于取放电路板不谨慎所造成的。这种不谨慎会使在取放、装配、测试和运输过程中遵守ESD注意事项所获得的好处付诸东流(见附文《ESD 敏感环境中的材料特性》)。一旦产品交付运输,你就无法加以控制,所以要精心设计电路板,尽量减小人体与元器件的无意接触。在电路板边缘布放一根接地的保护印制线,就可泄放掉因人体接触而引起的静电荷。电路板的布线应确保电路板上大多数相邻印制线间距符合良好的 CAD 惯例,使得ESD脉冲不会在相邻印制线间产生电弧并传播。

ESD 是对电子器件的一种威胁,也是造成器件失效的主要因素。消除由ESD 引起的失效要从各个层次全面着手,在设计、取放、装配、测试、系统集成、运输以及工作阶段均采用适当的 ESD 控制技术(见附文《在装配和生产中防备 ESD 效应》)。从来ESD 控制是一个持续的过程。器件尺寸的缩小和器件复杂性的增加都需要采用更新的 ESD 控制技术和失效预防技术,这些都将继续对电子设计师提出挑战。