LTM9002集成化双通道IF/基带接收器实例

引言对于任何希望在多通道IF采样或I/Q基带通信通道中进行高动态范围信号采样时充分利用ADC功能的设计师而言,拥有丰富的实践经验乃是至关重要的前提。要实现阻抗的匹配,需要熟悉放大器输出级和ADC前端的相关知识,而谨慎的布局则是实现数字输出至敏感模拟输入耦合最小化所必需的。

事实上,上佳的布局对于保持ADC性能是极其重要的,而始终苛刻的市场需求则迫切地希望实现设计的小型化,并提高通道密度,这加剧了布局问题。即使是最为老练的设计师,如果他擅长的领域是RF或数字技术,那么这些设计要求也会成为令其头疼的难题。

LTM9002双通道、IF/基带接收器利用了多年的应用设计经验,并将其整合在一个易用型11.25mm x 15mm μModule封装之内。该封装中内置了一个高性能双通道14位ADC (采样速率高达125Msps)、抗混叠滤波器、两个固定增益差分ADC驱动器和一个双通道辅助DAC。通过集成这些元件,LTM9002消除了输入阻抗匹配、滤波器设计、增益/相位匹配、通道间隔离和高频布局等工作负担,从而极大地加快了产品的面市进程。即使是在这种小型封装中,LTM9002仍然保证了高性能,从而将使诸多的通信和仪表应用得以强化。

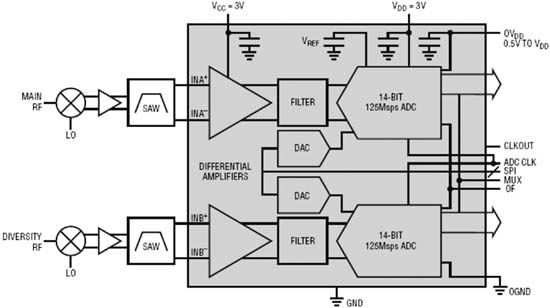

图1 用于主/分集接收器的LTM9002

多通道ADC应用

多通道应用具有多项独特的要求,例如:通道匹配 (在增益、相位、DC偏移以及通道至通道隔离度方面)。增益和相位误差直接影响着I和Q通道的解调。而且,由于直接转换接收器通常采用DC耦合,因此,DC偏移将限制接收器的动态范围。多输入、多输出 (MIMO) 系统依赖于多个均接收相同信号的接收器通道,并检测由多径延迟所引起的轻微变化,于是,增益和相位误差也会对这些系统产生影响。和I/Q接收器一样,分集接收器也需要在通道之间提供极佳的隔离,这是因为通道之间的串扰会表现为噪声干扰,而且可能更加难以利用数字滤波处理来抑制。显然,ADC和驱动器电路的通道匹配和通道隔离将直接影响系统级性能。对于许多多通道应用而言,这些误差是无法在数字域中进行校正的。

性能

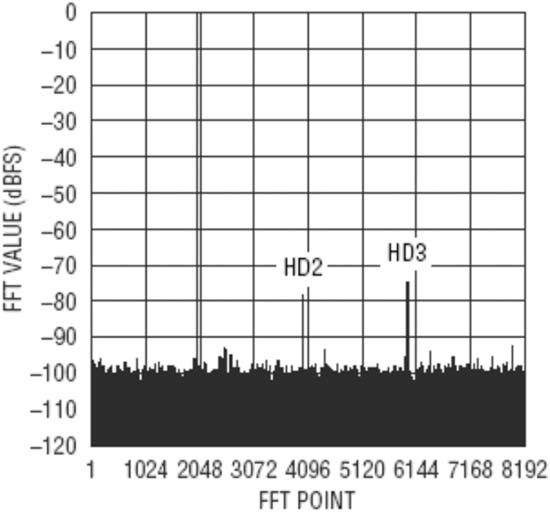

在140MHz的输入频率条件下,LTM9002实现了66dB的信噪比(SNR)和74dB的无寄生动态范围 (SFDR)。图2示出了这些条件下的FFT。SNR是ADC和放大器性能以及放大器增益和滤波器带宽的一个函数。固有放大器噪声与电压增益成比例;因此,26dB放大将使放大器噪声增加20倍,而8dB放大则仅使噪声增加2.5倍。同样地,放大器噪声(单位:nV/√Hz)随滤波器带宽的平方而增加。在评价整个信号链路时应牢记这些关系,这一点是十分重要。

图2 显示LTM9002 AC性能的FFT (采用140MHz输入频率)

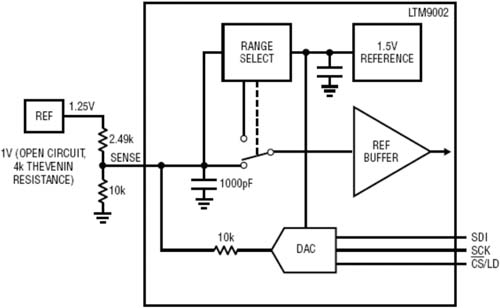

对于多通道应用来说,通道至通道匹配和隔离是重要的考虑因素。尽管外形尺寸小巧,但LTM9002仍然在140MHz的输入频率条件下实现了90dB的通道隔离度。在缺省的范围设定值条件下,总增益通常为26dB,而且在两个通道之间的变化仅为0.1dB。可对12位辅助DAC进行配置,以采用图3中的电路来调节范围 (每级的调节量为61μV)。

图3 采用一个外部基准和用于范围调节的内部辅助DAC

另一个重要的性能衡量指标是印刷电路板 (PCB) 的面积效率。在这方面,LTM9002胜人一筹。LTM9002不需要外部元件 (电源旁路电容器、无源滤波元件、阻抗匹配或变换元件等等都不需要)。在许多IF采样应用中,增益可以通过变压器来获得,但这些变压器常常体积庞大,而且难以采用自动化装配设备进行安装。在DC耦合应用中,与ADC驱动器一样,放大器及其相关联的抗混叠滤波器网络也是需要的。整个IF/基带接收器系统的占板面积达两平方英寸 (约为25mm x 50mm) 之多的情况并不少见。而当采用LTM9002时,不需要任何这样的外部电路,因此其所需的占板面积仅为1/4平方英寸左右 (11.25mm x 15mm),缩减至原来的1/8。

属性和配置

该μModule结构使得LTM9002能够把标准ADC和放大器元件混装在一起 (不管它们采用的是何种工艺技术),并使其与无源元件相匹配 (针对某种特定的应用)。μModule接收器由导线压焊芯片、封装组件以及安装在一块高性能、四层、双马来酰亚胺三嗪 (BT) 树脂衬底上的无源元件组成。BT与其他的层状衬底 (例如:FR4) 很相似,不过,其硬度十分出色,并具有较低的热膨胀系数。

LTM9002-AA使用了一个双通道、14位、125Msps ADC,两个26dB固定增益放大器,而且还包括一个针对全标度范围调节而配置的12位双通道DAC (如图1所示)。内部抗混叠滤波器负责将输入频率限制在 <170MHz。放大器提供了一个50Ω的差分输入阻抗和一个 ±50mV的输入范围 (即 -16dBm)。该缺省范围是通过把SENSE引脚连接至VDD来设定,并能够采用三种方式来调节。对于较低的 -3dBm 范围,可以将SENSE引脚连接至1.5V。通过把SENSE引脚连接至VDD或1.5V,内部基准即被采用。可以通过给SENSE引脚施加0.5V至1.0V的电压来使用一个外部基准。辅助DAC提供了一个用于选择范围的最终选项。或者,也可以利用外部基准或辅助DAC来对范围进行精细调节 (比如:平衡两个通道的增益)。

在多种节能模式当中,包括对放大器或ADC进行独立停用。ADC具有两种停机状态,即:NAP (打盹) 和SLEEP (睡眠) 模式。在打盹模式中,内部基准处于偏置状态,于是转换操作可在启动之后的100个时钟周期之内恢复。在睡眠模式中,基准被关断,启动操作需要1μs或更长的时间。该器件具有一种时钟占空比稳定器功能,并提供了一个输出时钟信号(用于准确地锁存输出数据)。两个通道可以在单独的并行总线上输出,或被复用至单根并行总线上(以节省处理器引脚)。

连接至模拟输入

LTM9002的模拟输入提供了一个50Ω的差分阻性输入阻抗,在大多数场合中,该阻抗都是与信号通路精确地匹配。输入共模电平应大约为VCC/2。传统上,ADC的输入需要极大地关注驱动电流、稳定时间以及对采样及保持开关操作的非线性特性响应。如欲实现最低的失真性能,则ADC输入的共模电平必须针对特定的ADC前端进行优化;如欲获得最佳的信噪比 (SNR) 性能,则信号摆幅必须利用最大ADC输入范围。在LTM9002的内部对此均有所考虑。

连接至数字输出

LTM9002采用了从OVDD切换至OGND的标准CMOS输出缓冲器。OVDD可在0.5V至3.6V的范围内变化,从而能够适应许多不同的逻辑器件系列,而OGND则可高达1V。由于LTM9002的电源是在内部进行旁路的,因此无需布设本机电源旁路电容器。用于数字输出缓冲器的电源应连接至负责给被驱动逻辑电路供电的那个电源。例如:如果转换器驱动一个由1.8V电源供电的DSP,那么OVDD应被连接至这个1.8V电源。较低的OVDD电压还有助于降低从数字输出至模拟或时钟电路的干扰。OVDD和OGND被与ADC电源和地隔离开来。一个与输出端串联的内部电阻器使输出表现为50Ω阻抗 (相对于外部电路),而且可以免除增设一个外部阻尼电阻器的需要。

电源和旁路

LTM9002需要一个3.0V电源,为了对LTM9002内部每个功能块的性能进行优化,采用了多个电源引脚。在内部,每个电源都被旁路至非常靠近芯片的地,旨在最大限度地降低耦合噪声。传统ADC电路板布局的一个常见问题是:由于从旁路电容器至ADC布设了很长的印制线,因而导致系统性能有所下降。在LTM9002中,采用内部旁路电容器的裸片结构提供了尽可能精确的去耦,并免除了增设外部旁路电容器的需要。

结论

多通道ADC应用需要实现上佳的通道至通道匹配和隔离,而不占用宝贵的板级空间。如果没有匹配、隔离和板级空间约束条件,那么驱动高性能ADC将具有相当的挑战性。LTM9002集成化双通道IF/基带接收器子系统设法满足了所有这些要求,并免除了使ADC与其驱动器相匹配的设计任务。通过集成无源滤波和电源旁路元件,其总尺寸比采用另外的分立型可实现方案时有了大幅度的缩减。LTM9002的μModule封装本身是专为最大限度地提高集成元件的性能而开发的。