PCI9030及其PCI总线接口电路设计

0 引 言

PXI总线系统的卓越性能和较低的价格,使得越来越多从事自动测试的工程技术人员开始关注PXI的发展。而PXI总线是PCI总线在仪器领域的扩展,可以将PXI总线分为PCI总线和PXI扩展的总线两部分。将进行PCI总线接口电路的设计,从而为设计 PXI模块仪器,组建PXI总线自动测试系统做好准备。

目前,PCI总线接口电路的实现主要有两种方案:一是采用一片大容量FPGA/CPLD实现PCI总线接口逻辑;另一种是采用ASIC芯片完成PCI总线的接口电路。由于PCI总线速度高,协议复杂,采用第一种方案虽然应用很灵活,但是调试困难,开发周期长,而且采用一片工业级可用于PCI接口的 FPGA/CPLD完成PCI总线接口功能,远比使用PCI接口芯片的成本高。采用第二种方案,功能强,价格低,稳定性好,开发周期较短。通过对上述两种接口方案的比较,从综合开发难度、芯片功能、开发速度和开发经费等方面考虑,在此采用后一种方案完成PCI总线的接口设计。

1 PCI9030芯片及其主要特点

PCI9030是全球最大的PCI接口设备制造商PLXTechnology于1999年3月推出的全新的32 b/33 MHz PCI目标设备接口芯片。它采用PLX先进的SMARTarget技术,不仅为各种应用提供了最大的灵活性,而且大大简化了系统设计,具有最高的性价比,能够满足各种应用的要求。PLX计划用它替代应用广泛的PCI9050和PCI9052。PCI9030主要有以下特点;

(1)采用PLX先进的SMARTarget技术,完全兼容PCI 2.2协议规范,PCI突发传输速率高达132 MB,/s,是第一个符合CompactPCI PICMG2.1标准的工业级目标设备接口芯片。

(2)支持高达60 MHz的局部总线操作,突发传输模式下速率可达240 MB/s,支持PCI目标预取模式、PCI目标可编程突发传输、PCI目标延迟写模式和PMW(Posted Memory Writes)模式。

(3)资源丰富,应用灵活。它支持5个PCI to Lo-cal地址空间,拥有9个通用I/O(GPIOs),4个可编程片选(CS[3…0]),中断发生器/控制器,支持 Big/LittleEndian字节转换,可提供PCI缓冲时钟(33 MHz),局部总线可编程读写选通定时等。

(4)局部总线的配置可编程,可支持复用或非复用模式的8位,16位或32位局部总线。

(5)PCI9030支持3.3 V,5 V电源容错,因此在采用5 V电源的CPLD时,不需要进行电平转换,可以直接连接,使得电路更加简洁。

2 PCI总线接口电路

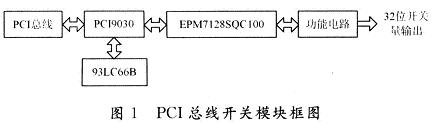

PCI总线开关模块是在满足PCI总线数据传输协议的前提下进行写数据和数据回读,完成PCI总线的基本数据传送。写数据时经过锁存和继电器驱动模块来驱动继电器工作,可以通过数据线回读继电器的状态,以判断数据传输的正确性,其原理框图如图1所示。

下面以本模块为例介绍PCI总线接口设计过程。

PCI总线接口电路主要分为3个部分,即PCI总线接口、局部总线接口、串行E2PROM接口,如图2所示。LCLK通过500 Ω电阻与BCLK0连接,为PCI9030提供本地时钟信号。局部总线多路复用和非多路复用选择是通过硬件实现。这里选用多路复用,故将PCI9030的 MODE引脚通过电阻上拉至3.3 V电源。边界扫描JTAG不使用,PCI9030引脚TRST应该通过电阻接地。