DNLMS滤波器的FPGA实现

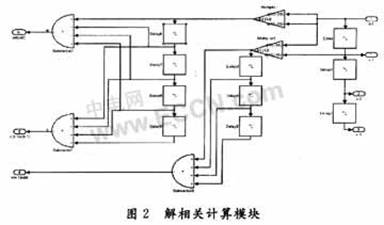

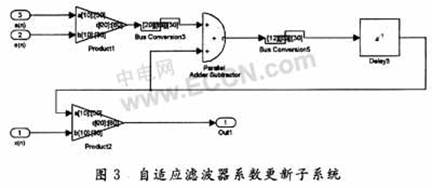

通过图2的优化,对于8阶滤波器,乘法块的使用从24个减少到2个,计算速度将得到很大的提高。ω的迭代运算通过图3实现。

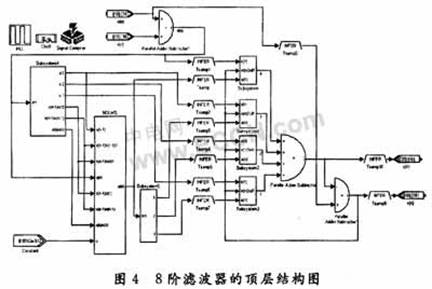

在顶层模块的设计中,加入了PLL模块和SignalComplier,根据各模块仿真周期,在PLL模块中设置好不同的周期,利用Simulink中的颜色标识采样频率的高低。顶层文件的设计如图4所示。

在顶层结构图中,子模块8为方程(9)的实现过程。

4 计算机仿真

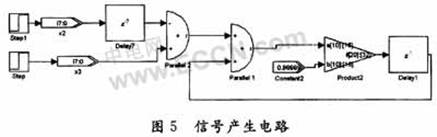

为了充分模拟相关性较强的信号,在输入端加如下的信号源:

x(n)=0.99x(n-1)+v(n)

式中:v(n)为高斯白噪声;x(n)的初始值为500,具体的产生电路如图5所示。

信号产生波形以及加噪后的仿真波形如图6所示。

通过滤波器滤波的结果如图7所示。

在图7的信号依次为参考信号、加噪声信号、误差信号和滤波信号。滤波效果良好,对于强相关的信号,也有很好的滤波效果。通过QuartusⅡ编译,滤器器的速度为35.24 MHz,编译后生产如图8所示的块,它作为一个符号模块可供更高级系统设计时调用,通过对该块的修改和增加滤波器的阶数,可以实现对语音的回声消除。

5 结 语

自适应滤波器的研究是近年来研究的热门方向,在PFGA中实现高速的自适应滤波器的设计更是一个热点,在此采用DSP Builder系统建模的方法,在FPGA中实现了归一化LMS算法,实验结果表明:用DSPBuilder设计的8阶DNLMS算法比用底层的VHDL代码设计效率更高,灵活性更大,速度更快。同样比通用的DSP芯片设计的8阶NLMS滤波器处理速度快了20多倍。如果将8阶NLMS滤波器扩展到512阶或者1 024阶,可以很好地应用于自适应回声消除等很多自适应滤波的领域。故有一定的参考价值。

相关推荐

在线研讨会

焦点