基于双单片机的信号处理系统设计

当检测与控制系统处理大量数据和多路信息时,只用一片单片机往往无法满足系统实时性和扩展性要求,且处理时间较长。例如在液面信息采集过程中,单片机要在相等的时间间隔进行A/D转换以及数据处理。由于要实现高通量的液体操作,液体操作平台通常配置多根移液针同时进行液体操作工作,采集多路液面信息。因此这里提出一种基于双单片机的信号处理系统设计方案,该系统采用单片机(AT89S51)作为核心器件,2片AT89S51型单片机作为双核心分担整个检测单元的任务。

1 系统硬件电路设计

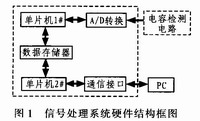

该信号处理系统的总体设计方案为:单片机1定时进行A/D转换,并且将转换结果存入外部数据存储器:单片机2读取数据存储器中的转换结果并且通过串口传递给计算机,同时还负责在系统接收到开始或停止命令之后相应开始或停止单片机1的A/D转换工作。图1为该信号处理系统的硬件结构框图。

根据上述设计方案,该系统硬件分为以下模块:

1.

由于AT89S51单片机并没有A/D转换模块,因此在采集系统中需要使用具有A/D转换功能的器件,这里采用ADC0832。ADC0832是美国国家半导体公司生产的一种8位分辨率、双通道A/D转换器。其主要特点如下:输入输出电平与TTL/CMOS相兼容;5 V电源供电时输入电压在0~5 V之间;工作频率为250 kHz,转换时间为32μs;一般功耗仅为15 mW。

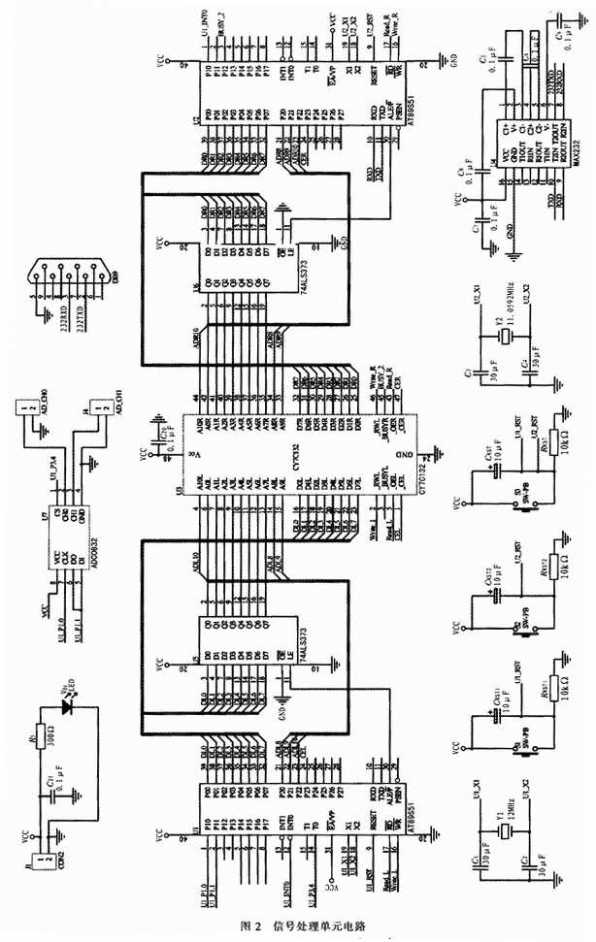

A/D转换模块设计采用了ADC0832的以下引脚:引脚1(CS)是片选使能信号端,接单片机AT89S51的P3.4引脚。引脚2(CH0)、引脚3(CH1)是2个模拟量输入通道,由于检测器只使用了一个电容传感器,因此,这里只采用引脚3作为模拟量输入。引脚5(DI)是数据信号输入端,负责选择通道控制。引脚6(DO)是数据信号输出端,负责输出转换后的数据。引脚5和引脚6由于在通信时并不是同时有效,而且与单片机是双向接口,所以在使用过程中将这两引脚连在一起使用,并连接至单片机的P1.1引脚;引脚7(CLK)是芯片时钟输入,接至单片机的P1.0引脚,如图2所示。

1.2 存储模块设计

通过对存储器性能、价格、购买情况等因素的综合考虑,该系统设计采用Cypress公司的CY

CY

该系统设计采用存取时间为55 ns的CY

2 具体电路设计

根据上述系统总体结构框图和功能设计,绘制信号处理系统的电路原理图,如图2所示。

单片机的控制或检测工作是通过I/O引脚实现的。单片机1(U1)中,PO和P2引脚以及P3.6与P3.7引脚用来与外部数据存储器CY

CY

另外,基于以下原因,单片机1与单片机2使用了不同频率的外部晶振:1)单片机AT89S51支持的频率有限,被选择的晶振频率必须符合要求;2)由于AT89S51使用机器周期作为其工作基准,在使用外部振荡电路的情况下,该单片机是以晶振频率除以12得到的数值作为机器周期,所以在单片机1需要定时器的情况下,晶振频率要便于定时器的设置;3)单片机2需要和计算机进行串口通信,晶振频率要便于串口通信中波特率的设置。因此,单片机1与单片机2的晶振频率分别选择了12 MHz和11.059 2 MHz。