基于FPGA的8PSK软解调的研究与实现

表1 是通过MATLAB 仿真平台计算出来的每个Eb/N0所对应的误码率,图2 是与之相对应的误码率曲线图。由图2 可知,对于Eb/N0 测试区间为4 dB 到7 dB 的任意一个测试点,LLR 最优算法的误码率总比定点MAX 算法和浮点MAX 算法要小,其中浮点MAX 算法误码性能居中,定点MAX 算法最差。MAX 算法是通过降低误码性能来换取运算复杂度的降低,其误码性能要比LLR 最优算法差。与浮点MAX 算法相比,定点MAX 算法对输入软解调模块的I、Q两路信号和输出的似然比分别进行了截位和限幅,如图2 所示,定点MAX 算法相对于浮点MAX 算法损失了一定的误码性能。由表可知,定点MAX 算法在Eb/N0 为6.64 dB 时,其误码率为6.5125×10-8,验证了该定点方案能够满足系统设计要求。

表 1 MATLAB 误码率仿真表

图2 MATLAB 误码率仿真

3 MAX 算法硬件实现

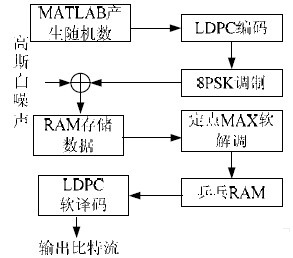

由于硬件实现都是定点运算,所以MAX 算法的实现是针对定点的MAX 算法进行硬件设计的。硬件仿真流图如图3 所示,首先利用MATLAB 产生随机序列,假设每一编码块为4032 bit,LDPC 编码效率为1/2 码率,则经过LDPC 编码后,每一编码块为8 064 bit,经8PSK 调制成符号后,每一个编码块被调制成2 688 个符号,实部虚部分为I、Q 两路,再叠加信噪比为SNR 的高斯白噪声,最后把数据文件存储在RAM 中。在硬件实现上,定点MAX 软解调模块以一定速率从RAM 读取数据并进行软解调,软解调输出的对数似然比存储在乒乓RAM 中,每存满一个编码块就向LDPC 译码器发出一个读有效信号,LDPC 译码器在接收到该有效信号的下一个时钟周期就开始以一定速率读取整个编码块的对数似然值,接着开始进行LDPC 译码,最后以一定速率输出最终的译码结果。

图3 硬件设计仿真

4 硬件设计结果分析

验证一个软解调模块性能的好坏,需要级联译码模块进行仿真综合验证。在硬件设计中,通过在Stratix II FPGA 硬件平台上级联MAX 定点算法模块与LDPC 译码算法模块,然后进行综合布线,最后下载到硬件平台进行测试。

将仿真通过的工程文件使用Chipscope 添加观察采样信号,触发信号和待观察信号后重新综合、布局布线生成bit文件,下载到目标板后用Chipscope 进行在线测试,通过将输出结果与输入比特流进行比较,验证设计正确性。分析QUARTUS II 综合报告,该设计模块只需加减法器,部分寄存器和16 个乘法模块,使用资源较少,能满足低复杂度、高吞吐量的设计要求。

5 结语

由于LLR 算法具有较高的运算复杂度,不易于硬件实现,而经过简化的MAX 算法由于避免了指数和对数运算,大大降低运算复杂度,只需进行加减法和少数乘法运算,适合于硬件实现。该设计通过MATLAB 与VHDL 仿真对照,验证了MAX 软解调算法硬件设计的准确性,同时将该模块与LDPC 译码模块级联,在具体的FPGA 芯片上运行,利用片上分析仪Chipscope 进一步验证设计的可行性。