高性能与低功耗:FPGA上可以实现鱼与熊掌兼得

10月20日,Altera SOPC World 2008深圳站开幕,来自珠三角地区的近500位工程师参加了这一探讨“高性能与低功耗设计”的技术盛宴,由于参加人数众多,现场一度发生拥堵现象。本次大会上,Altera不但抢先披露了将今年年底提供工程样片的新的40-nm Stratix® IV FPGA一些细节,更和合作伙伴一起发布了有关利用FPGA实现高性能与低功耗设计的方案,并探讨了Cyclone® III FPGA和MAX® IIZ CPLD一些最新应用,大会传达了这样的信息:在FPGA领域,高性能和低功耗是可以实现鱼和熊掌兼得的。

FPGA与全球金融危机中的本土公司发展

“在这次席卷全球的金融风暴中,中国不可能独善其身,面对金融风暴,本土制造企业要做的利用核心知识产权来创新。”Altera中国区销售经理钟屹在致辞中指出,“我们本土企业中华为、中兴和迈瑞是三家利用独有知识产权创新的典范,本土企业可以利用这次机会,在逆境中前进。”

具体到企业的运营,他指出本土企业首先要做的就是首先是要用最小的成本实现最大的收益,另外就是要了解如何提升企业的生产率,如何去实现创新。而这三点又恰恰和FPGA有关,他强调Altera为助力本土企业实现上述目标提供了所需的高中低所有产品,12月Altera 40nm Stratix® IV将面市,会给客户带来更多创新的功能和设计。

做为本土创新的典范之一,中兴通讯天线研究院BBU研发中心算法部部长张睿结合中兴通讯的实际介绍了自主知识创新的体会和对未来技术演进的预测,他指出,“中兴在标准和专利领域非常活跃,目前专利申请总数14800余项,90%以上为发明专利申请,国际专利申请超过1100项,此外中兴还加入50多个国际标准化组织,牵头、参与制定的国家、行业标准和企业标准900多项,参与率90%!”

他强调,目前电信运营商最关注如何降低总拥有成TCO(total cost of ownership),要满足运营商这些需求,就需要在基站的站点数量、低功耗设计、升级成本、土建成本等方面节约成本,而落实到基站设计上,就是要实现高集成高效率基站设计。例如GSM从传统的单密度到双

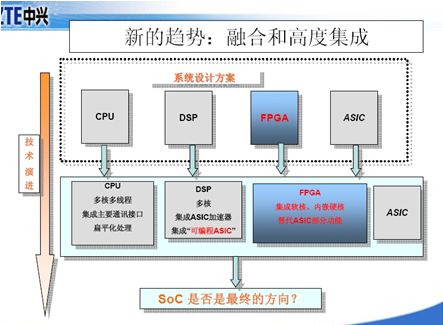

密度、四密度,多载波进一步提高基站集成度,单机柜从支持6载频到18、36载频等。这样就促使CPU、DSP、FPGA、ASIC放弃原来独立演进的路线,逐步发展为互相渗透式的“融合和高集成”式演进,例如DSP向多核发展,并融合ASIC,而FPGA开始集成软核和硬核并取代ASIC部分功能,这样发展下去,“SoC会终结这个趋势吗?。”他提出了这样的问题。

什么样的FPGA可以成为SoC终结者吗?

就像要回答他的疑问,Altera亚太区副总裁兼董事总理Erhaan Shaikh在题为《多处理技术提高性能、降低功耗》的演讲中指出未来电子应用不但需要更有效地电源管理,更需要高性能,为了满足这个双重的需要,业界需要更灵活的技术,而FPGA是理想的解决方案。

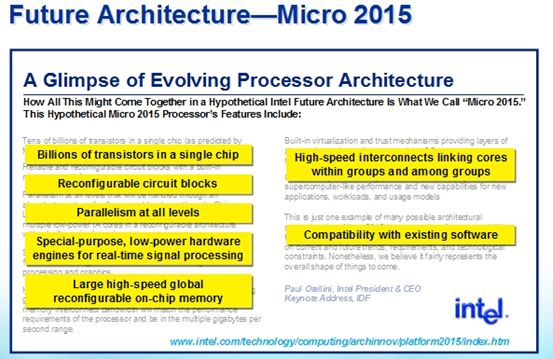

移动通信和互联网极大地丰富并方便了我们的生活,但是,这样的便利带来了是能源的消耗加剧。他举例说目前一个柴油发电基站每年需要消耗5238加仑柴油,以每加仑4美元计算,消耗的柴油就超过2万美元。但是,全球互联网带宽消耗却是每年在快速增加,迫使需要投入更多的电信设备,现在产业已经达成共识,就是利用多核体系来应对性能提升需求。Intel CEO曾经勾画了未来处理器的雏形,它“单个芯片中有数十亿个晶体管、可配置电路模块、所有层次上实现并行、专用低功耗引擎实现实时信号处理、大规模高速全局可配置存储器、与现有软件兼容。。。。”

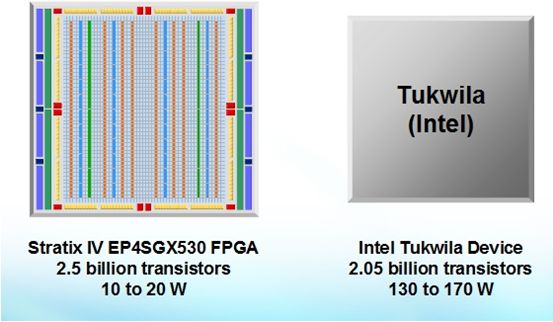

Erhaan Shaikh指出现在有一个器件可以吻合这个构想中的处理器,它有“23亿个晶体管、700万可配置逻辑门、所有层次上实现并行、嵌入式DSP实现748GMACS计算性能、超过1000个的I/O管脚实现组内和组之间可以高速连接、可配置片内存储器高达22Mb,36Tbps带宽,可以利用标准HDL设计和综合”,这就是即将面市的Stratix® IV EP4SGX530 FPGA!与Intel的Tukwila相比,它真正实现了高性能与低功耗――拥有25亿个晶体管的Stratix® IV功耗只有10到20瓦!而同等性能的Intel Tukwila功耗达130到170瓦!

Stratix® IV 大揭秘:如何兼得高性能与低功耗

Erhaan Shaikh对Stratix® IV的描述无疑勾起与会者对其性能的猜想,这到底是一款什么样的FPGA?Altera南中国区工程应用经理郭晶和 Altera资深应用工程师花小勇为大家揭开了Stratix® IV神秘的面纱。

1、 Stratix® IV性能指标揭秘

Stratix® IV是密度最大的FPGA,它有高达680K的LE,有高达22.4Mbits的内部RAM

拥有1,360个18 x 18乘法器!它有最大的带宽,32个收发器,工作在600Mbps和8.5 Gbps 之间,另外16个收发器模块,工作在600Mbps和3.2 Gbps 之间,有320Gbps全双工贷款以及优异的信号完整性。花小勇指出:“Altera在Stratix® IV上实现了收发器创新,并增强了功能,例如有可配置的第五和第六全双工通道,通道绑定最多为24个通道,支持SFI-5和HyperTransport3.0协议,而且收发器设置、数据速率和洗衣运行时间都是可重新配置的。”

他指出动态可重新配置不需要额外的软件开销并减少线卡开销,因此可以帮助系统商降低成本。

在收发器中,jitter和信号完整性是关键指标,在Stratix® IV中,抖动指标符合PCI Express、CEI-6和SONET/SDH指标,并有余量,并内置预加重和均衡,可驱动6.375Gbps的50英寸FR-4背板。

花小勇特别指出目前只有Altera提供即插即用的信号完整性,当PVT变化时,可以监视并优化接收均衡。

Stratix® IV的另一大特色是提供大量经过预验证的复杂IP硬核模块,包括X8、X4、X2、X1 PCI Express2.0规范兼容内核,集成TL、DLL、PHY/MAC和收发器等,“这些硬核可以省下40k的逻辑单元,而且因为这些硬核不用编译,所以可以不考虑时序限制。”他指出。

花小勇指出Stratix® IV也有最好的存储器接口,实现了1067Mbps/533MHz的DDR3智能接口模块,可以具有PVT自动校准功能。此外,Stratix® IV的动态片内端接可以节省1瓦的功耗(72I/F),它还有丰富的存储器带宽支持416Gbps(333MHz)、463Gbps(400MHz)、556Gbps(533MHz)等新一代应用。