高性能与低功耗:FPGA上可以实现鱼与熊掌兼得

另外,Stratix® IV采用了大量的硬核IP来降低功耗,而且不消耗设计中的编译资源。

不过,他指出,最有效降低功耗的还是Altera 的Hardcopy技术,它可以将布线功耗降低95%、

逻辑减小80-90%、RAM减小35-65%!

Cyclone® III FPGA和MAX® II也有高性能与低功耗

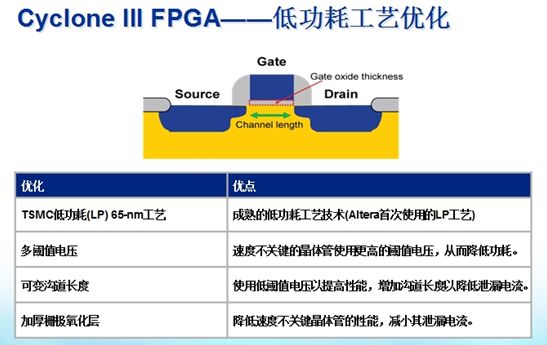

郭晶强调,Altera已经全面将低功耗技术应用到高中低所有器件系列上,在Cyclone® III FPGA和MAX® II上也同样实现了高性能与低功耗。下图就显示了Altera在Cyclone III上采用的低功耗工艺技术。

当然,在MAX II上也有类似的技术,MAX IIZ CPLD静态功耗降低到29微安,动态功耗也只有8.9毫安。在这次大会上,Altera的合作伙伴Echelon公司介绍了基于Altera CycloneIII低成本控制网络方案。这些方案应用在商业、工业和消费领域,不但性能可靠,也完全实现了低功耗低成本的目标。其他合作伙伴则展示了基于Altera的电信、安防、汽车电子解决方案等。

此外,Altera行销产品经理张洵瑜还介绍了MAX IIZ在模拟应用的案例,她指出,CPLD除了完成逻辑功能外,还可以应用在模拟电路中,例如可以利用MAX II上拉电阻来测量电容,不需要外部元件。采用MAX II还可以完成触摸开关应用、阻性触摸屏、容性触摸屏、辐射和亮度测量、LED闪烁控制等需要模拟器件完成的设计。

相关推荐

u-blox助力AddMobile实现「连网建筑工地」服务

行业应用

2019-09-04

在线研讨会

焦点