高性能与低功耗:FPGA上可以实现鱼与熊掌兼得

除了有出色的DSP性能以及强大的嵌入式处理器,Stratix® IV另一个重要特点是采用了优化的机构体系,其自适应逻辑模块(ALU)可以在更短时间完成逻辑操作。花小勇指出FPGA个更关注功效的概念,就是每瓦功率达到的最大性能,单方面追求性能最大化没有实际意义,利用Altera的可编程功耗技术可以将非关键路径的功耗降低,实现功效最大化。与同类级别的FPGA相比,Stratix® IV不但性能出众,而且功耗降低很多。

2、 Stratix® IV低功耗技术解密

那么,Stratix® IV是如何实现高性能下的低功耗呢?郭晶指出Altera通过六大技术降低了FPGA的功耗,这六大技术是:

1、 使用高级工艺,并进行功耗优化。

2、可编程功耗和加速电路

3、降低供电电压(Stratix® IV的内核电压降低到0.9 V)

4、硬核知识产权(IP)

5、降低电感和电容(LC)的设计方法

6、封装技术

而在功耗和性能优化方面,实际是贯穿了从工艺到IC设计、IC开发、系统开发的整个流程。如下图所示。在工艺技术方面的优化,不是简单地将65nm升级到40nm,实际上牵涉到更多技术,例如在工艺技术方面就采用了硅片搀杂、三次门氧化、电压供电电平、金属互联等技术。

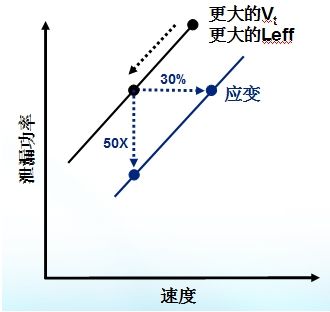

实际上,在Stratix® IV中,还采用了称为应变硅的工艺技术,它的好处是电子和空穴移动能力提高了30%,泄漏功率不变,速度提高约30%。速度不变,Ioff降低约50倍!

值得一提的是Stratix® III中的可编程功耗技术仍应用在Stratix® IV中,它和Quartus® II软件 的PowerPlay功耗分析功能一起,可以大幅度降低FPGA的动态功耗和静态功耗。可编程功耗技术不是将没有使用的资源关断。在具体实现中,Quartus软件会决定哪些电路(晶体管)应处在高速(HS)模式和低功耗(LP)模式。通过调整背向偏置电压来改变阈值电压,减小非关键时序通路上的晶体管泄漏 (提高阈值电压),从而在需要的地方降低功耗,提高性能。

可编程功耗技术是内置在Stratix III器件芯片中的体系结构创新,当某些电路不需要高性能时,Quartus II软件可以改变晶体管阈值电压来控制功耗 (通过每一电路域的余量来确定)。这是除了关断Stratix III FPGA中未使用资源(例如,时钟树)的另一方法。

“这是Altera独有的技术,并获得了专利。不需要用户参与。由Quartus软件在每个设计中自动完成。”他特别指出。

他指出在设计中,所有未使用的逻辑也被设置为低功耗模式。通过使用低功耗逻辑,静态功耗降低了70%。Quartus II根据用户时序约束,将每个逻辑单元自动设置为高速或者低功耗模式。这没有改变用户的开发流程。

Stratix® IV其他降低功耗的技术有Stratix III中使用的动态片内匹配(OCT)技术,其不同之处在于动态接通/关断,这对通用总线接口特别有用,例如DDR等。在存储器写期间(FPGA输出缓冲驱动存储器芯片),接通串联电阻,匹配走线阻抗,关断并行匹配终端,降低功耗。在存储器读期间(存储器芯片驱动FPGA输入缓冲),可以匹配传输线。当缓冲在输入和输出之间切换时,Stratix® IV自动完成这一过程,反之亦然。