移动设计转向MIPI

新的移动智能电话和便携式移动互联网设备(MID)设计正在越来越多地利用新一代处理器的低功耗和高性能特性。在这些移动应用中,新的平台能够实现诸如高清视频捕获、高分辨率双相机、更高显示分辨率和支持同时多显示屏等带宽密集型功能。本文将概述能够满足这些大带宽功能的、日益流行的移动行业处理器接口 (Mobile Industry Processor InteRFace,MIPI) 架构的功能性;此外还将探讨在单个应用设备中,利用高性能模拟开关在两个器件之间共享高速MIPI路径的优点和设计考虑事项。

在当今世界,高科技手持式设备广为流行,你或许会以为并行数据接口是一件过时的东西。毕竟这种架构已面市数十年,对于如今关注小尺寸、低功耗、功能丰富的市场来说,它不再被视作未来发展的候选技术。然而,仍有许多新型移动电话和MID设计继续采用这种旧有接口,因为它是应用处理器的唯一可用接口。

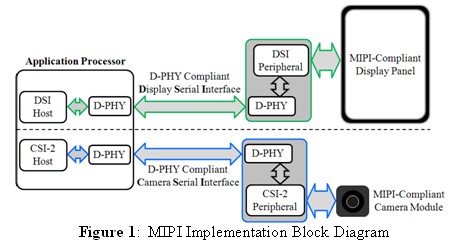

当前,终端市场要求新设计具有更低功耗、更高数据传输率和更小的PCB占位空间,在这种巨大压力之下,一些智能化且具有更高性能价格比的替代方案开始逐渐为相关设计人员所采用。现在使用的几种基于标准的串行差分接口当中,MIPI接口在功率敏感同时又要求高性能的移动手持式设备领域中的增长极为迅速。而基带和显示器/相机模块对MIPI显示器串行接口(Display Serial Interface,DSI) 和相机串行接口(Camera Serial Interface,CSI-2)协议的广泛采纳,正是这种增长的主要推动力。DSI 和 CSI-2是分别针对显示器和相机要求的逻辑层(logical-level)协议,它们通过物理互连对主机与外设之间的数据进行管理、差错和通信。 MIPI D-PHY规定了连接处理器和外设的物理层的物理及电气特性,这些MIPI接口为服务移动设备市场而专门设计。图1所示为显示器与相机路径上的MIPI接口的顶层模块示意图。

图1:MIPI实现方案模块示意图

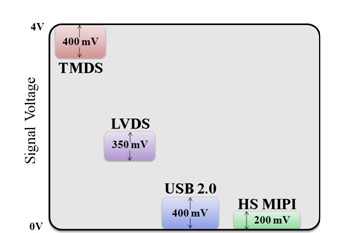

这里举两个MIPI获大规模采纳的例子,包括两大主流芯片组制造商英特尔(Intel)和Marvell都在它们最新的移动芯片架构中集成了MIPI功能,英特尔的Moorestown处理器和Marvell的Armada 600处理器都采用了基于MIPI标准的 DSI 或 CSI接口。MIPI 架构可通过减少其差分串行接口中的I/O 数目来降低处理器的引脚数目及功耗,故是当仁不让的最佳选择。动态可调的低功耗 (LP) 和高速 (HS) 数据模式以及高速模式下的低信号摆幅(signal swing),也可为MIPI 提供比单端接口更好的EMI辐射性能和EMI抗扰性能。此外,由于连线减少,PCB设计灵活性得以提高,从而能够改进连接器或外设器件的布局。虽然这些优点为许多串行接口所共有,但MIPI 是专门在高速(数据传输)模式下采用低振幅信号摆幅,针对功率敏感型应用而量身定做的。图2比较了MIPI与其它差分技术的信号摆幅。

图2:几种流行的差分摆幅(differenTIal-swing)技术的信号振幅比较

这种架构的另一个主要特性是可扩展性。MIPI规定了一个差分时钟通道(lane)和一个从1到4数量可扩展的数据通道,可根据处理器和外设的需求来调节数据率。而且,MIPI D-PHY规范只给出了数据率范围,并没有规定具体的工作速率。在一个应用中,可用的数据通道和数据率都由接口两端的器件决定。不过,目前可用的MIPI D-PHY IP内核可提供每数据通道高达1 Gbps的传输率,这种特性无疑意味着MIPI完全适用于当前及未来的高性能应用。