电子产品面板控制芯片的后端设计

2.4 时钟树综合

由于同步设计电路中所有的操作都需要时钟控制来实现同步,而时钟网络在所有信号网络中负载最大、走线最长、要求最苛刻,因此时钟树综合的质量直接影响芯片的性能。时钟树综合的目的在于控制时钟传播延迟、时钟偏移和跳变时间。较大的时钟延迟对解决电路的建立时间问题不利,较大的时钟偏移会增加寄存器锁存不稳定数据的几率,而控制好跳变时间有利于优化时钟树的功耗。本设计先采用在自动CTS模式下,根据时钟树规格文件中的时序约束自动决定级别数和缓冲器数,然后根据设计中的具体情况用手动方式修改级别数、缓冲器类型以及所连接的寄存器,以达到尽可能好的效果。通过比较时钟树综合报告文件可知,在自动模式下,时钟偏移为0.13 ns,通过手动修改后时钟偏移为0.078 ns,时钟树综合结果显示,如图3所示。

2.5布线

SOC Encounter在布线时分为两个阶段完成:预布线和详细布线。预布线时布线工具把整个芯片划分为多个较小的区域,布线器只是估算各个小区域的信号之间最短的连线长度,并以此来计算连线延迟和每个区域的布线拥塞程度,这个阶段并没有生成真正的版图连线。详细布线时考虑信号完整性和时序驱动,同时可修复天线效应、串扰影响和设计规则违反。详细布线工具寻找并修复短路和开路的线,同时完成布线后优化。在详细布线时,Routing Track定义,布图规划,setNanoRouteMode命令参数设置的冲突会引起线的开路。出现开路情况后使用verifyTracks命令可以诊断标准单元的线的开路问题,能报告出在Blockage内部引脚的距离太远,引脚未对齐,引脚在Stripes下面等问题。通过对报告分析,了解原因后进行布局调整直到解决问题。

2.6 可制造性设计

可制造性设计包括消除天线效应(NEC0.35CZ6H工艺不需要)、加Core填充单元(FILL1,FILL2)、优化接触孔、加金属填充满足金属密度要求。

默认情况下是使用单孔进行上下层之间的连接,在空间允许的情况下可使用双孔或多孔进行连接,使用双孔或多孔的目的是减少过孔电阻、减少电迁移引起的失效,有利于时序收敛和提高良率。布线工具会利用:Multiple-cut Vias或Fat Vias替换掉信号过孔达到优化过孔的目的。详细布线时利用插入Multi-Cut Via或Fat Vias修复串扰。

版图是由一行行等高Row组成,由于Row放置标准单元的利用率不可能达到100%,因此在Row中标准单元之间可能会有大小不等的间隙,这些间隙若不用填充单元进行填充,则在物理验证工具进行设计规则检查时会产生大量DRC违规,解决办法是加Core填充单元(FILL2,FIL-L1)。

根据CZ6H工艺中的金属密度填充规则对所有金属层加入考虑时序的金属填充,这样可尽量避免在时钟和信号线周围加入金属填充,而更多的是加在电源和地线周围。

2.7 验证

对执行可制造设计后的版图进行连线验证和时序验证。连线验证包括:线是否连上(Verify Connectivity)、网格是否正确(Verify Geometry)、金属密度是否达到20%等等,运行后可以检查报告文件,发现金属填充后存在的线与线间距的违规,需要手工进行调整。

时序验证产生报告来检查建立时间、保持时间、最大电容和最大过渡时间是否满足要求,本设计满足要求。

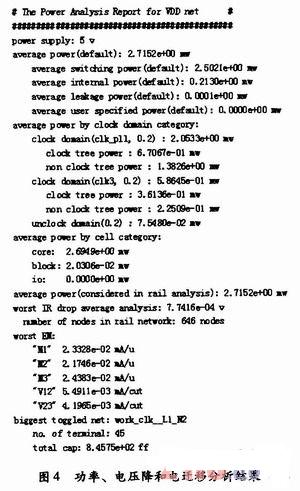

2.8 功耗、电压降和电迁移分析

对设计好的版图进行功率、电压降和电迁移分析结果如图4所示,从中可知使电源/地PAD数量、电源环、电源条的设计符合功耗、电压降、电迁移要求。

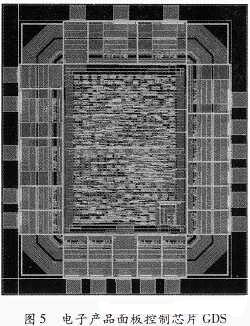

2.9 输出

版图设计完成后,要从版图中提取进行后端验证所需的信息,如用于形式验证、物理验证、静态时序分析和后仿真的Verilog网表文件,用于物理验证工具进行。DRC,LVS和LPE的经过各单元GDS文件Merge后输出的GDS文件。将产生的GDS文件导入Virtuoso Layout Editor工具加入Cover单元并在相应的位置打上Labe1标号,最终电子产品面板控制芯片的版图,如图5所示。

3 结束语

对SoC Encounter输出的版图和网表,用Formality工具进行形式验证,用Star-RCXT工具提取寄生参数后用PrimeTime工具进行静态时序分析,用物理验证工具Calibre进行DRC和LVS,采用Modesim进行流片之前的后仿真,本设计通过上述的所有验证,成功试制小规模样片,利用搭建的测试台对样片进行验证证明达到了设计的要求。