循序渐进精通Blackfin系列DSP

Blackfin系列DSP是著名的通用DSP厂商ADI公司与Intel公司联合开发的一种基于微信号结构(MSA),兼有DSP和通用微处理功能的处理芯片。从性价比上看,与其它厂商同类DSP相比,Blackfin系列DSP仍具有独特的优势,它的应用已越来越多,越来越广泛。那Blackfin系列DSP有什么样的特点呢?如何入门和开发呢?这里以Blackfin基本型BF53x系列DSP来说明。1. 先了解外围接口及内核

这是了解DSP的第一步。BF53x提供了较多的接口,如SPORT、SPI、PPI、UART、SDRAM、GPIO、定时器/计数器等接口。这部分主要是硬件设计和驱动设计必需要掌握的,这方面内容较多,资料也很多,可以上网查寻,也可在书店购买相关书籍,不过最好是看ADI公司提供的Blackfin器件手册。这里主要对BF53x内核作简要说明。

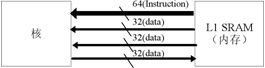

BF53x内核主要由ALU、寄存器、L1 SRAM(内存)组成。ALU与寄存器算是核心。它们连结大致如图一所示。

图一 BF53x内核组成图

核可以对内存进行64位数据或指令读取,但写只是能32位以内。这意味着我们可进行长指令或宽数据的处理。而且内存与核是工作在同频的。如果我们进行的是每个周期都只是8位数据运算,我们将浪费大量内核的总线资源和处理能力。那么我们如何充分利用内核这些资源呢?

2.了解Blackfin系列DSP的指令

通过对指令的认识可以更加了解内核,同时也为实际开发练好基本功。这里只对部分单周期多操作指令作简单介绍。

(1)2对16位数运算指令。如:R3=R0+|-R1; R3=abs R1(v); R3=R3>>n(v)等等。

(2) 4对8位数运算指令。如:BYTEOP1P,BYTEOP2P,BYTEOP3P,BYTEOP16P,BYTEOP16M,BYTEPACK,SAA,BYTEUNPACK等。其中SAA为视频编码算法的运动补偿中的方差求解提供了极大方便。BYTEOP1P、BYTEOP16M为视频块搜索和运动补偿中的二进制插补提供了方便。

(3)丰富的单周期位元指令。如ONES指令对奇偶校验十分有效,免去了循环;bitmux指令可以有效解决数字信号处理卷积算法和FFT算法中的位反序寻址问题;BXORSHIFT, BXOR指令可以用于线性反馈移位寄存器与多项式相关的乘除法。

(4)码元/字段抽取指令:DEPOSIT与EXTRACT、ALIGN8, ALIGN16, ALIGN24可以极大方便视频叠加与分解算法和视频数据打包运算。

(5)比选指令VIT_MAX可用于Viterbi译码蝶型算法中关键部分加比选单元的处理;

(6)并行处理指令。采用分隔符||来实现运算存取数并行进行。如:R3.H=(A1+=R0.L*R1.H),R3.L=(A0+=R0.L*R1.L) || R0=[I0++] || R1=[I1++];

SAA(R1:0, R3:2) || R0=[I0++] || R2=[I1++];

这种并行指令是64位的,可以充分利用内核指令总线带宽和内核处理能力。

(7)单周期完成判断和跳转指令:

IF CC JUMP destination;

IF !CC JUMP destination;

(8)零开销循环指令:LSETUP和LOOP。零开销不是指令执行不需开销,而是指循环一次结束到下次循环开始之间无延迟,相当于顺序执行一段连续代码一样。利用pipeline viewer工具我们可以很清楚的看到这一点。

Blackfin系列DSP还有较多其它指令,这些指令的设计都是针对内核高处理能力和宽总线的。平时应多使用这些单周期多操作指令。刚开始不太熟悉指令,很可能想不起来。但我们如果经常用,慢慢就会熟悉起来了,一定不能有畏难想法。不能使用DSP指令汇编的工程师肯定不是合格DSP工程师!

3.编程练习

编程首先要安装VisualDSP++开发环境,建议采用4.0及其以后的版本,不要装3.5及以前的,因为高版本支持性更好,安装完VisualDSP++,PCI和USB仿真器等驱动都会跟着装完。第一次打开VisualDSP++时,会要求License,一般随光盘都会提供一个,主要是测试用的(正式的需上ADI网申请)。选取具体DSP器件及仿真方式(硬件/软件),就可以像打开Visual C++6.0一样的界面出现了,之后便可以开始编程了。

安装目录下通常有各DSP芯片开发板的样例程序。建议刚开始在软件仿真环境下先看汇编例子,并试着修改编译,这可巩固和加深对前面指令的学习。同时要了解汇编程序的编写规范。了解这些后就可试着新建一个工程并编一小段代码编译。在单步调试时还可打开pipeline viewer、cycles寄存器、profiling等工具进行查看单周期多操作指令单步执行情况。这期间要多看VisualDSP++的帮助文件,它提供了全面详细的资料。

在对汇编认知有一定基础上,便可进行C语言方面的学习和编写了,相对汇编而言,C语言大家更熟悉,所以其学习时间不长。但要提醒的是:C语言循环体内要尽管少用条件语句;多用局部数据变量和局部指针变量,不用全部变量和指针;循环步长为1,不要跨步。这样在优化时编译器比较容易转换为硬件循环指令。

知道了汇编和C语言编程,还有一点是必须要知道的:一个工程中既有汇编又有C语言怎么相互调用呢?VisualDSP++提供了两种方式:

(1)在C语言环境下可以交叉使用汇编:ASM(” ”)。如:

ASM(”nop;”);

ASM(“r0=%0;”::”b”(x):”r0”);//对r0赋值

(2)对汇编函数块调用,默认参数传递变量是R0、R1、[FP+20]、[FP+24]…。

另外,ADI提供了很多C语言库函数,这些函数很多都是事先优化好的。要多调用。它们基本上都在VisualDSP++安装目录下各芯片系列的include目录下可找到。另外ADI还提供了很多图像压缩方面的样例程序,有做这方面的工程师也应多看看。

在软件仿真差不多的情况下,需要进行硬件仿真,就是用仿真器在实际硬件(如:开发板)环境中调试和运行程序。之后,便可在Project Option中设置生成ldr文件,并重新编译。编译通过后,ldr文件就生成了。

4.固件烧写

ldr文件可用于仿真器写入Flash,但需要驱动。而实际应用中,硬件设计常驱于选用更易购买且成本更低的Flash芯片。不同厂家和不同型号的Flash会引起驱动的不一样。在VisualDSP++安装目录相应DSP型号开发板样例里有一个Flash Programmer目录工程,可对之适当修改,以适应实际用的Flash特点,然后生成下载驱动可执行文件dxe即可。下载固件入Flash后就可以脱离仿真器运行了。

到这一步,对DSP的学习是不是够了呢?不,下面还有很多呢。

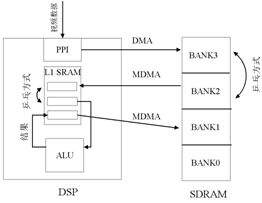

5.BF53x系列处理器总线结构

很多时候处理瓶颈往往不在内核的处理速度和能力上,而是数据交换上。频繁的数据交换会对总线造成巨大压力。这就像工厂生产能力很强,但原材料及货物运输很慢,就会引起工厂一边休息一边工作,而运输却一直很忙。ADI为这一点已做了不少努力。从图二中我们可以看到处理器内部有好几种总线。DMA总线就有三大类:DEB、DAB、DCB。它们与通用接口总线PAB和内外存储器之间总EAB并列,同时外部PPI口与存储器接口分离。这种总线形式,可以让内核在运算和外部数据传输同步进行。

图二 BF53x系列DSP内部总线图

Blackfin系列DSP的DMA有如下特点:

(1)DMA通道多:8个外围接口DMA和4个存储器DMA;

(2)支持链状DMA,所谓链状就是把表示需要多个传送的多组描述符放入一个链表中。当链表中前一个DMA完成后,自动启用链表中后一个DMA,不需处理器干预,自动进行;

(3)支持二维DMA,适合块数据拷贝;

如果多个DMA传输同时进行,DMA总线会不会相互冲突呢?只要不饱合,就不会。一是外设DMA均配有FIFO;二是有专门的DMA控制器进行调度管理。寄存器DMA_TC_PER和DMA_TC_CNT就是用于这种传输的管理(就像操作系统进程时间片轮换管理一样);三是对各通道DMA规定了默认优先级。8个外围接口DMA饱合传输率是每2个系统时钟传输一个16位数据,优先级可以重新设置;而4个存储器DMA饱合传输率是每1个系统时钟传输一个16位数据,优先级低于外围接口DMA,且不能重新设置。另需说明的是在编写外围接口驱动时,DMA数据最好打包,这样可以节约总线带宽,减少总线竞争。就像搬东西时,每次多搬点,从而可减少搬的总次数。

Blackfin53x内部总线内容还很多,这里只能是个大概。掌握了上面所说的内容后,我们还需了解什么呢?

6.分析Blackfin处理器存储器的结构

BF53x系列DSP均采用L1 SRAM(内存)加SDRAM(外存)方式。其对内存的设计颇费心思。内存容量不多,但访问速度与核一样,因而非常珍贵。BF53x系列DSP内存除了可以像外存一样存放数据和指令外,还具有数据Cache和指令Cache功能。如果充分利用好两种Cache功能,并合理分配数据高速缓存,可以极大提高处理速度。内外存的合理使用离不开对LDF文件的编写。LDF文件是连结描述文件意思,主要用于为各编译好的模块分配存放空间,以组成一个可执行或下载的文件。LDF文件的编写规范在VisualDSP++的帮助文件里都有很详细的说明。

7.应用实例分析

在明白和会使用上面所说内容后,应该可以进行一些项目的参与设计了。这里将对一个实时视频压缩MPEG-4方案进行说明。

目前大多数VGA图像传感芯片都能做到60fps和50fps。如果我们采用CIF格式,则在不影响图像质量的情况,我们可以每隔一帧采样一张图片,从而做到30fps或25fps,这同样不影响视觉效果。这意味着图像采集实际只需一半时间就可以了。采集过程采用PPI DMA方式存入SDRAM中,通过二维DMA和链表DMA完成从SDRAM中取数据到内存和重排(重排很简单,主要是通过修改DMA步长和目标指向即可)。SDRAM一般都有4个Bank,考虑到对同一个bank来回读写会增加页切换开销。所以应采用乒乓存取方式。这种方式内外存均要使用。外存某一Bank在存入图像数据时,而从另一个Bank读取数据,来回反复进行。内存采用乒乓方式与之类似,当某一块正在存入外面进来已重排好的图像数据时,另一块正在被内核编码处理,处理完后又反过来。这种方式可以达到并行处理。再配上Cache功能,就可以达到比较理想的结果。

图三 BF53x实时图像压缩流程

以上例子只是一个系统设计思路,实际中会有一些差异。目前,用BF53x作CIF格式的MPEG-4实时编码和用BF561作D1格式的MPEG-4实时编码均已有不少成功案例。

总之,Blackfin系列DSP为设计人员提供了很多内部资源,这些资源能否得已充分利用,以及如何合理利用,都对设计人员提出了更高的要求。可能有些功能从不会用到,但了解是必要的。其强大的处理能力是综合性的,它体现在内核速度、指令形式、总线、内存、Cache、外围接口等多个方面。ADI公司在BF53x的基础上又衍生了多种DSP,它们就像一本厚厚的书,需要设计工程师较长的时间去消化,去认识。

相关推荐

在线研讨会

焦点