台积电:14nm制程节点将用垂直型晶体管结构

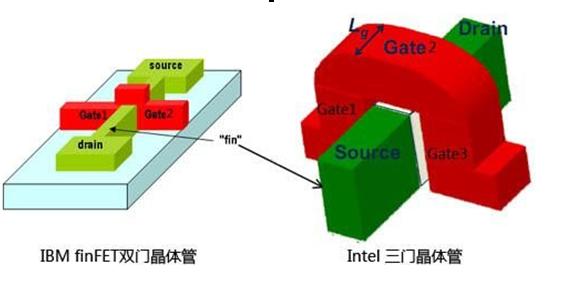

据参加了比利时微纳米电子技术研究机构IMEC召开的技术论坛的消息来源透露,与会的各家半导体厂商目前已经列出了从平面型晶体管转型为垂直型晶体管(以Intel的三栅晶体管和IBM的FinFET为代表)的计划。

其中来自半导体代工巨头台积电公司负责研发的高级副总裁蒋尚义在会上发言称,台积电公司已经决定在14nm制程节点转向使用垂直型晶体管结构。

蒋尚义表示:“经过研究,我们决定在14nm制程节点放弃使用传统的平面型晶体管结构,转而采用能更好控制沟道性能的垂直型晶体管结构。”据他表示,台积电会先从28nm制程进化到20nm制程,然后将于2015年左右的时间点直接进化到14nm制程。

与此同时,IMEC新建的

IMEC公司高管Thomas Hoffmann表示:“眼下向我们过问FinFET制造问题的芯片设计公司已经越来越多。”他认为由于Intel据称会在22nm制程节点开始采用垂直型晶体管技术,加上台积电也已经表态支持这种晶体管结构,因此引起了这些设计公司的注意,大家都想提前为这种技术做好足够的技术准备。

“我们和我们的客户都很想搞清楚Gate-last工艺能在FinFET晶体管中发挥出怎样的实际性能,对那些有意在22/16nm制程转向FinFET晶体管结构的公司来说,他们很想知道如果放弃传统的平面型晶体管结构,那么会对现有的high-k/金属栅极技术产生什么样的影响。”

Intel公司率先在45nm制程节点开始启用Gate-last工艺来制作HKMG晶体管,而台积电也将在28nm制程节点开始启用这种工艺。Hoffmann认为Gate-last工艺具有许多优势,比如PMOS管的门限电压更为稳定,而且这种工艺将原来填充在栅极区的多晶硅替换为金属材料时,还可以为PMOS管的沟道施加一定的应变力。

不过以IBM/ GlobalFoundries/三星等Fishkill技术联盟为代表的阵营这坚守Gate-first工艺,他们宣称Gate-first工艺制造的晶体管密度更大,更有利于芯片核心的小型化。

在这种情况下,不少需要依赖代工厂的芯片设计公司也是举棋不定,他们频繁与两方阵营往来接触,比对双方两种不同HKMG制作工艺的优缺点。

Hoffmann表示:“对28nm制程低功耗芯片而言,采用gate-frist工艺已经完全可以满足技术要求。”