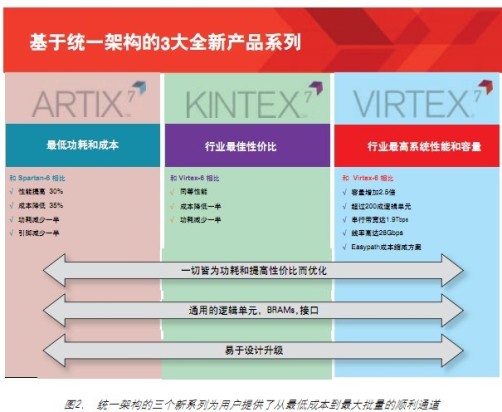

三大系列28nm器件成功融入主流高端ASIC和ASSP市场

Peng指出,除了能够给客户和IP合作伙伴带来重大优势,该统一架构还能让赛灵思今后的开发工作更加重点突出、分工明确。Peng表示:“这意味着我们的企业可以一次性完成相关工作。”

28nmHPL:功耗、容量和性能的完美组合

随着新款7系列的推出,赛灵思通过与台湾晶圆厂TSMC合作,引入了最新优化的高k金属门(HKMG)高性能、低功耗(HPL)工艺,完成了制造策略的调整,使之进一步与现代IC设计的实际情况相结合。

过去,FPGA厂商都是在晶圆厂推出最新的半导体工艺之后,立即在其性能最高的变种上实施设计。不过,从90nm工艺开始,漏电就成为一个严重的问题。而且该问题针对65nm和40nm更为严重。在28nm工艺节点上,如果不加以处理,漏电电流将占器件功耗的50%以上。除了在器件没有工作的时候还耗用电力,运行时的漏电电流还会产生额外的热量,而这种热量会进而加重漏电。特别是对连续使用的高性能应用而言,这种恶性循环会缩短器件的寿命,导致灾难性的IC故障。这会严重影响在给定应用中使用FPGA的可行性以及系统的可靠性。

在限制28nm的高性能工艺的漏电问题上,晶圆厂已经取得了重大进展。赛灵思与其新的晶圆厂合作伙伴TSMC合作,针对7系列对该厂的新款HKMG HPL工艺进行了优化,重点是在缩小几何尺寸的同时提高容量和系统性能,同时降低功耗。

Peng表示,通过用HPL工艺取代HP工艺,赛灵思可以将功耗降低50%,而性能方面的降幅只有3%。通过融合HPL工艺与在7系列中实现的综合性强化节能措施,与上一代密度相同的产品相比,可以让总体能耗下降50%。

Peng表示,50%的能耗下降可以带给设计小组两个选择:“在7系列中以此前一半的功耗实现类似规模的Virtex-6或者Spartan-6设计,或者在[新]设计中以相同的功耗实现双倍的逻辑功能。采用HPL工艺后,我们可以为客户提供更加具有可用性的性能和更多的逻辑门,以便在设计中实施更多的功能。”

赛灵思首席执行官Gavrielov指出,通过选择更高容量但更低功耗的28nm工艺产品,赛灵思跟上了微处理器行业的步伐,进而引领FPGA行业的发展。大约10年以前,MPU制造商就认识到采用更新的工艺来提升时钟频率会造成严重的漏电问题,从而导致耐热性差的器件损坏。

Gavrielov表示:“我们从半导体行业的处理器侧了解到,鉴于目前的工艺情况,更高的集成度和效率是实现性能的最佳途径,而非仅仅提高器件的运行速度。采用当前的工艺,如果只是单纯地提高运行速度,会消耗更多的功率,并带来散热问题——从而恶化功耗水平和性能。我们需要高度关注最终用户应用,确保我们在满足系统的低功耗要求和系统需求之间寻得合理的平衡。我们认为,随着深受客户青睐的7系列FPA的推出,我们将交付出色的价值方案。”

Peng指出,如果赛灵思采用HP工艺实现增量时钟加速,与功耗的大幅度增加相比,性能的增加将显得微不足道,从而迫使用户在设计中把许多精力放在功耗和散热问题上。他们可能需要在最终的系统中采用复杂的散热装置,甚至于风扇或者水冷系统以及相关的供电线路,从而造成额外的系统成本。