加快和简化串行数据测试

串行数据流的速度不断提高,而误码规范也越来越严格,这使抖动容差性和误码率(BER)测试变得越来越重要。几位工程师以不同方式解决了这个问题,但是结果相似——他们全都缩短了测试时间,降低了设备成本。

David Andres 是 Marvell Semiconductor 公司的一位设计工程师,提出了一种可加快串行/解串器(SerDes)接收器 BER 测试的方法;Chung Wu 是 Maxim Integrated Products 公司的产品定义师,运用眼图模板来定义 SerDes 接收器的性能;Christopher J. Loberg 是 Tektronix 公司市场开发高级经理,利用波形发生器来创建测试信号。

Andres 花了数年时间来评估 SerDes 接收器。在那段时间,他开发了一种技巧,使他在测试数十个器件时,可以将接收器测试时间从数小时缩短至数分钟。在为 Marvell 的其他工程师构建其他评估系统时,他还发现了一些简化测试设置和降低成本的方法。

一些客户要求 Andres 针对低达 10–18 的 BER(每 1018 个比特的误码少于 1 个)进行测试,但大多数客户均要求验证每 1012 个比特的 BER。在这些误码比率下,速度为 2.5Gbps 的完整 BER 测试可能需要 6 分 40 秒。为了获得 99% 的“不会出现一个比特误码”置信度,Andres 需要对每个器件运行至少 100 次 BER 测试,总测试时间超过 11 个小时。

由于 Andres 一般要为新设计、变更的设计、需要抽查的设计测试多达 50 个器件,因此需要缩短测试时间。通过设置一项提高误码出现概率的测试,Andres 可把每个器件的测试时间缩短至数秒。加快的测试为他带来了足够的“被测器件(DUT)将达到可接受的 BER 性能”的置信度。

添加时序变化

为了加快测试,Andres 为数据流添加了数量受控的时序变化(抖动),使抖动与眼图模板规范重叠。在一项应用中,他利用 7 比特伪随机比特序列(PRBS7),在眼图模板内为每 127 个比特产生了 4 个边沿。添加的抖动产生了足够的时序变化来预测接收器的性能。他还利用了 PRBS23、PRBS31 和其他比特模式。

Andres 结合两种技巧为串行数据流添加受控的抖动:过采样和混频。过采样需使用速度四倍于相关比特率的模式发生器。他使用 10Gbps 模式发生器来构建 2.5Gbps PCI Express(PCIe)Generation 1 数据流。

为了从 10Gbps 信号得到稳定的 2.5Gbps 数据流,Andres 用 4 个连续1(或十六进制的单个 F)得到了 2.5Gbps 的单个的1比特,2.5Gbps 的单个 0 比特则是由 10Gbps 的 4 个连续的 0 比特得到的。然后,他移动边沿时序来创建抖动。

Andres 说:“借助 10Gbps 模式,就能把任何上升沿或下降沿的时序改变 0.25 个单位间隔(UI)。利用两个边沿,就能为信号添加 0.5 UI 的抖动。还可以在模式中改变最差情形抖动的位置。测试人员可以检查许多不同位置,然后向设计师提供反馈,说明模式中的弱点出现在何处。DUT 在一个方向能处理的抖动比另一个方向高得多。”

图 1 展现的是Andres 做法。上方的轨迹表明 2.5Gbps 的 4 个比特(1010),没有添加抖动(边沿未移动)。在 10Gbps 时,模式是由十六进制 F0F0 表示的。下方的轨迹是 2.5Gbps 的一系列 4 比特(1,0,0,1),但 0 比特和随后的 1 比特之间的上升沿提前 0.25 UI 出现了。

Andres 的实现方法是在 10Gbps 利用十六进制 1(二进制 0001)来代替二进制 0000 后接十六进制 F(二进制 1111)。通过反复改变比特模式,Andres 能在 2.5Gbps 流中创建抖动。

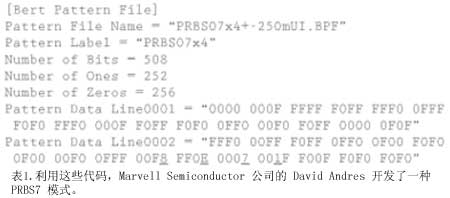

表 1 列出了 Andres 用于开发 PRBS7 模式的代码。Pattern Data Line0002 中带有下划线的 4 个数字表示被缩短或延长 0.25 UI 的比特。例如,“8”表示前一个比特的延迟下降沿,而“E”表示后一个比特的提前下降沿。

过采样过程没有为 Andres 提供足够的抖动以达到测试 PCIe 接收器所需的 0.65 UI 抖动。图 2 表明当比特边沿侵入眼图模板(钻石)时,就会出现误码。Andres 利用混频来添加正弦抖动(Sj),以便覆盖其余部分。事实上,他能产生足够的时序变化来完全闭合眼图。

图 2 中标明闭合眼图宽度的光标对应于比特边沿之间的 39 皮秒时间,并表示眼图闭合。波形上方的直方图表明边沿时序的分布。抖动覆盖大约 53 皮秒的范围,抖动的其余 14 皮秒来自数据相关抖动(DDj)和随机抖动(Rj)。Andres 说:“我不喜欢随机抖动,因为它很难量化和调试。随机抖动随着测量时间的延长而增加。”