新开发FinFET整合III-V族与矽材料

比利时微电子研究中心(IMEC)宣称开发出全球首款在300mm晶圆上整合III-V族与矽晶材料的3DFinFET化合物半导体。IMEC的新制程目标是希望能持续微缩CMOS至7nm及其以下,以及实现混合CMOS-RF与CMOS光电元件的化合物。

随着晶片微缩即将接近原子级的限制,业界致力于提高晶片性能与降低功耗的各种方法逐渐面临瓶颈。透过为矽晶整合更高性能的材料,例如可提供更高载子速度与更高驱动电流的III-V族电晶体通道,这种新的化合物半导体可望超越矽晶本身性能,持续微缩至更制程。

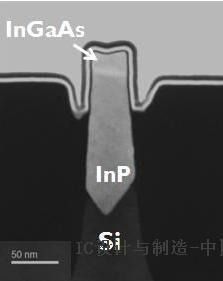

首款在300mm晶圆制造的III-VFinFET电晶体,采用磷化铟(InP))与砷化铟镓(InGaAs)化合物。

英特尔(Intel)与其他公司已在尝试结合III-V族材料(如砷化铟镓与磷化铟)与传统矽晶基板的化合物半导体了,但一直无法克服材料之间原子晶格难以匹配的挑战。而今,IMEC声称已经成功实现一种晶圆级制程,透过撷取晶体缺陷的长宽比、沟槽结构与外延制程等创新,能够以砷化铟镓与磷化铟等材料在3DFinFET上取代矽鳍,同时还能适应8%的晶格不匹配。

「基本上,我们经由FinFET制程至鳍片形成阶段,以特定的蚀刻制程从选定的鳍片移除矽晶,蚀刻的图案能让III-V族生长以及吸收缺陷,」IMEC逻辑研发总监AaronThean解释,「我们开始加进III-V族材料,先从磷化铟开始,使其吸收约8%的晶格不匹配,使其最终生长至顶部,然后在凹处再次加进磷化铟,并以砷化铟重新生长至顶部。」

据Thean表示,IMEC的合作夥伴希望这项技术能进一步开发,以期能在2016年到2018间实现7奈米节点的部署。IMEC的CMOS开发合作夥伴将有机会取得该制程,包括英特尔、三星、台积电、Globalfoundries、美光、海力士、东芝、松下、Sony、高通(Qualcomm)、Altera、富士通、nVidia与Xilinx。